Package Information

| Lead Count (#) | 28 |

| Pkg. Code | MWV |

| Pitch (mm) | 1.27 |

| Pkg. Type | SOICW |

| Pkg. Dimensions (mm) | 17.93 x 7.52 x 0.20 |

Environmental & Export Classifications

| Pb (Lead) Free | No |

| ECCN (US) | EAR99 |

| Moisture Sensitivity Level (MSL) | |

| HTS (US) |

Product Attributes

| Lead Count (#) | 28 |

| Carrier Type | Reel |

| Pb (Lead) Free | No |

| Temp. Range | 0 to +70°C |

| Bias Voltage Range (V) | 12 - 12 |

| DDR Capable | No |

| Input Voltage (Max) (V) | 5 |

| Input Voltage (Min) (V) | 5 |

| Length (mm) | 17.9 |

| Linear Output | Yes |

| MOQ | 1000 |

| Output Current 1 (Max) (A) | 25 |

| Output Voltage (Min) (V) | 1.05 |

| Output Voltage 1 (Max) (V) | 1.825 |

| Output Voltage 2 (Max) | 1.2 (Adj.) |

| Output Voltage 3 (Max) | 1.5 (Adj.) |

| Output Voltage 4 (Max) | 1.8 (Adj.) |

| Outputs (#) | 4 |

| Parametric Category | Multiphase DC/DC Switching Controllers |

| Pitch (mm) | 1.3 |

| Pkg. Dimensions (mm) | 17.9 x 7.5 x 0.20 |

| Pkg. Type | SOICW |

| Qualification Level | Standard |

| Switching Frequency Range (Typical) (kHz) | 200 - 200 |

| Thickness (mm) | 0.2 |

| Width (mm) | 7.5 |

Resources for ISL6524

Description

Support is limited to customers who have already adopted these products.

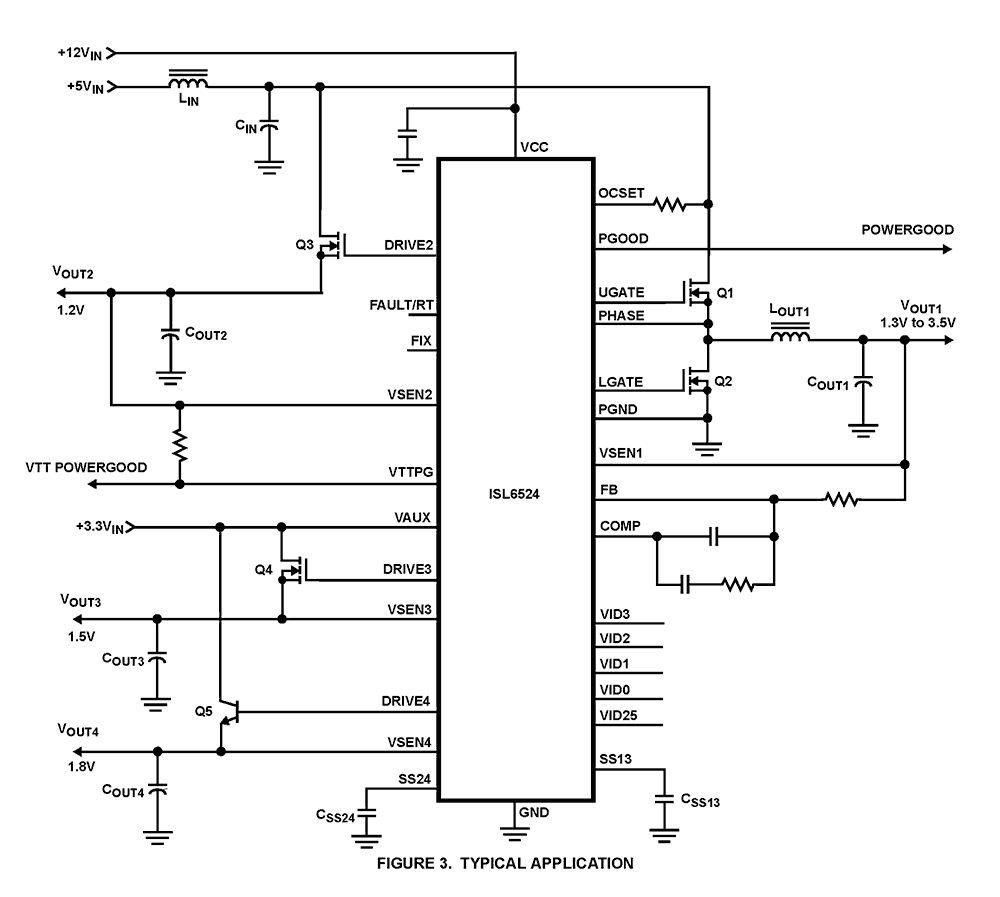

The ISL6524 provides the power control and protection for four output voltages in high-performance microprocessor and computer applications. The IC integrates one PWM controller and three linear controllers, as well as the monitoring and protection functions into a 28-pin SOIC package. The PWM controller regulates the microprocessor core voltage with a synchronous-rectified buck converter. One linear controller supplies the computer system's AGTL+ 1. 2V bus power. The other two linear controllers regulate power for the 1. 5V AGP bus and the 1. 8V power for the chip set core voltage and/or cache memory circuits. The ISL6524 includes an Intel VRM8. 5 compatible, TTL 5-input digital-to-analog converter (DAC) that adjusts the microprocessor core-targeted PWM output voltage from 1. 050V to 1. 825V in 25mV steps. The precision reference and voltage-mode control provide ±1% static regulation. The linear regulators use external N-channel MOSFETs or bipolar NPN pass transistors to provide fixed output voltages of 1. 2V ±3% (VOUT2), 1. 5V ±3% (VOUT3) and 1. 8V ±3% (VOUT4). The ISL6524 monitors all the output voltages. A delayedrising VTT (VOUT2 output) Power Good signal is issued before the core PWM starts to ramp up. Another system Power Good signal is issued when the core is within ±10% of the DAC setting and all other outputs are above their under- voltage levels. Additional built-in overvoltage protection for the core output uses the lower MOSFET to prevent output voltages above 115% of the DAC setting. The PWM controller's overcurrent function monitors the output current by using the voltage drop across the upper MOSFET's rDS(ON), eliminating the need for a current sensing resistor.