Overview

Description

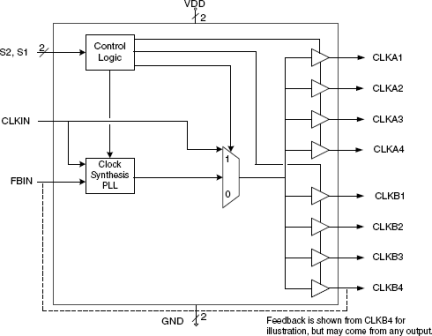

The MK2308-1H is a low phase noise, high-speed PLL-based, 8-output, low skew zero delay buffer. Based on Renesas' proprietary low jitter Phase-Locked Loop (PLL) techniques, the device provides eight low skew outputs at speeds up to 133MHz at 3.3V. The outputs can be generated from the PLL (for zero delay), or directly from the input (for testing), and can be set to tri-state mode or to stop at a low level. For normal operation as a zero delay buffer, any output clock is tied to the FBIN pin.

Features

- Clock outputs from 10MHz to 133MHz

- Zero input-output delay

- Eight low-skew (< 200 ps) outputs

- Device-to-device skew < 700ps

- Full CMOS outputs with 25mA output drive capability at TTL levels

- 5V tolerant FBIN and CLKIN pins

- Tri-state mode for board-level testing

- Advanced, low-power, sub-micron CMOS process

- Operating voltage of 3.3V

- Industrial temperature range available

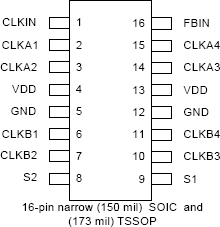

- Packaged in 16-pin SOIC and TSSOP packages

- Pb (lead) free package

- Industrial and commercial temp operation

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: