Overview

Description

The 662-03 provides synchronous clock generation for audio sampling clock rates derived from an HDTV stream. The device uses the latest PLL technology to provide superior phase noise and long term jitter performance. The device also supports a 27 MHz output clock for video MPEG applications from an HDTV reference clock. Please contact IDT if you have a requirement for an input and output frequency not included here.

Features

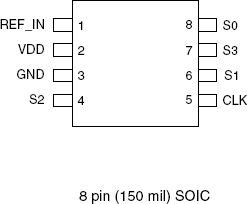

- Packaged in 8-pin SOIC

- Pb (lead) free package, RoHS compliant

- HDTV clock input

- Low phase noise

- Exact (0 ppm) multiplication ratios

- Support for 256 and 384 times sampling rate

- Supports 27 MHz output for video (MPEG)

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: