従来のソフトウェア開発手法の限界

- ソフトウェアの肥大化と開発手法の変化

車載向けのソフトウェアは日々肥大化しており、従来の開発手法では開発がすでに追いつかなくなってきています。例えばエンジン制御では、燃費向上や排気ガス規制に対応するためのきめ細やかな制御は、年々高性能化、高効率化が求められます。それを実現するためコード数は加速度的に増えていきます。

従来の開発手法に代わり、開発工数の削減、生産性向上、流用性の向上、開発精度の向上の必要があり、モデルベース開発(Model Based Development)によるソフトウェア開発に注目が集まっています。

- モデルベース開発について

モデルベース開発とは、開発の対象を数理モデル化し、作成したモデルを用いてシミュレーションを繰り返し行い、制御やシステムを作りこむ開発手法です。車載向けソフトウェア開発では急速に広がっています。モデルベース開発では、設計したモデルを用いてすぐに検証が行えるため、従来の開発手法で問題となっていた、検証工程での後戻りを防ぐことができます。

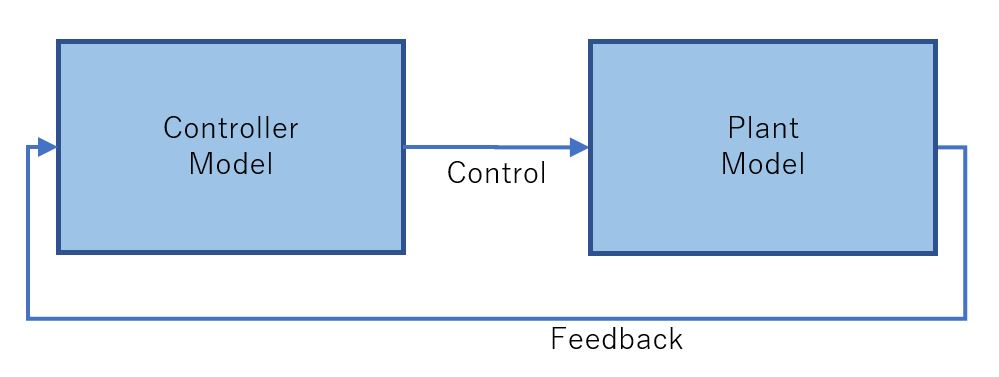

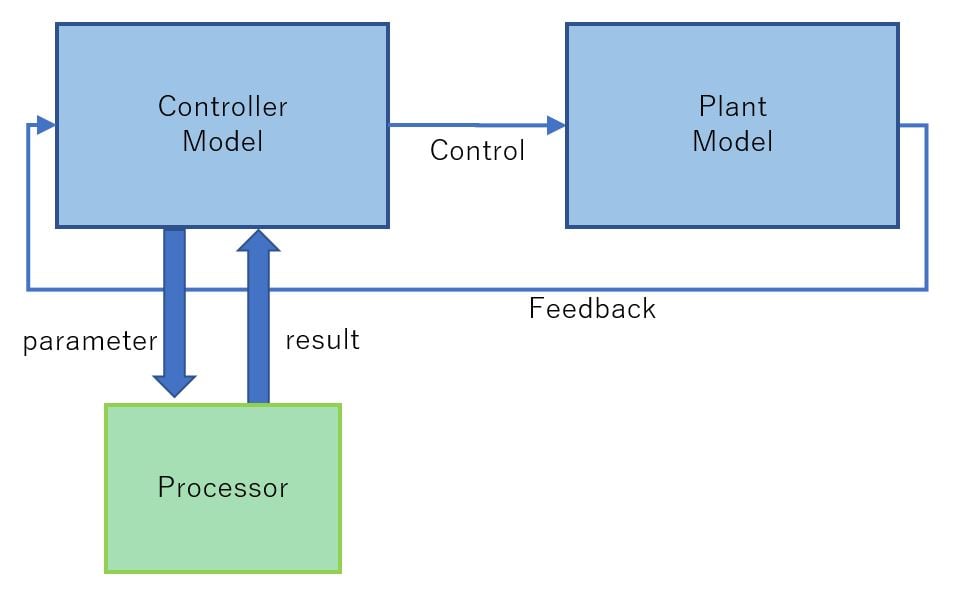

モデルベース開発では、制御(コントローラ)と制御対象(プラント)をモデル化し、作成したモデルでシミュレーションを行います。モデル上で行うシミュレーションをModel In the Loop Simulation(MILS)と呼びます。設計の早い段階で、MILSによるシステム検証を行うことが可能です。

このモデルの検証では、モデルから生成したコードを使用したシミュレーションの実行結果と、モデルによるシミュレーションの実行結果が同じであること確認し、生成したコードが正しいことを確認します。このようなテストをBack-to-Backテストと呼びます。

また、生成したコードをMCUなどのプロセッサで動作させて、モデルとプロセッサの連携シミュレーションを行うことで、アルゴリズム検証を行うことができます。 モデルとプロセッサを連携して行うシミュレーションをProcessor In the Loop Simulation(PILS)と呼びます。

モデルから生成したコードをMCU上で簡単に動作させるには?

モデルベース開発を導入してモデルを作成し、作成したモデルからコードを生成してBack-to-Backテストを行おうとしても、実際に生成したコードをビルドしMCUで動作させて、デバッガなどを設定しモデルと連携シミュレーションを手作業で行うのは時間のかかる作業です。また環境を立ち上げても、その動作や性能の解析が容易ではありません。

ルネサスのEmbedded Target for RH850 Multicoreは、MathWorks社Embedded Coder?と連携してMCU上で動作するコードを生成し、生成したコードをビルドしてデバッガにダウンロードして実行し、モデルとデバッガを接続して連携シミュレーションを行うことで、PILSを行うことができます。

- Embedded Target for RH850 Multicoreとは

RH850でPILSを行う環境を構築するためのソフトウェアです。

Embedded Target for RH850 Multicoreは以下の機能があり、PILSの環境を自動で構築することができます。

- ルネサス統合開発環境CS+(*1)のRH850用プロジェクトファイルの自動生成

- MathWorks社Simulink?のモデルからMathWorks社Embedded Coderによるコード生成

- CS+プロジェクトへのソースコードファイルの登録

- ビルドツールの設定

- デバッグツールの設定

- デバッガの起動

- Simulinkとデバッガの接続(サイクル精度シミュレータ(*2)か評価ボードが使用可能)

Simulinkとデバッガを接続後、Simulinkのシミュレーションを行うと、MCUとのPILSが行えます。Back-to-Backテストでは、PILSの実行結果とMILSの実行結果が同じになることを確認します。

*1 https://www.renesas.com/cs+

*2 https://www.renesas.com/rh850-cycle-accurate-sim

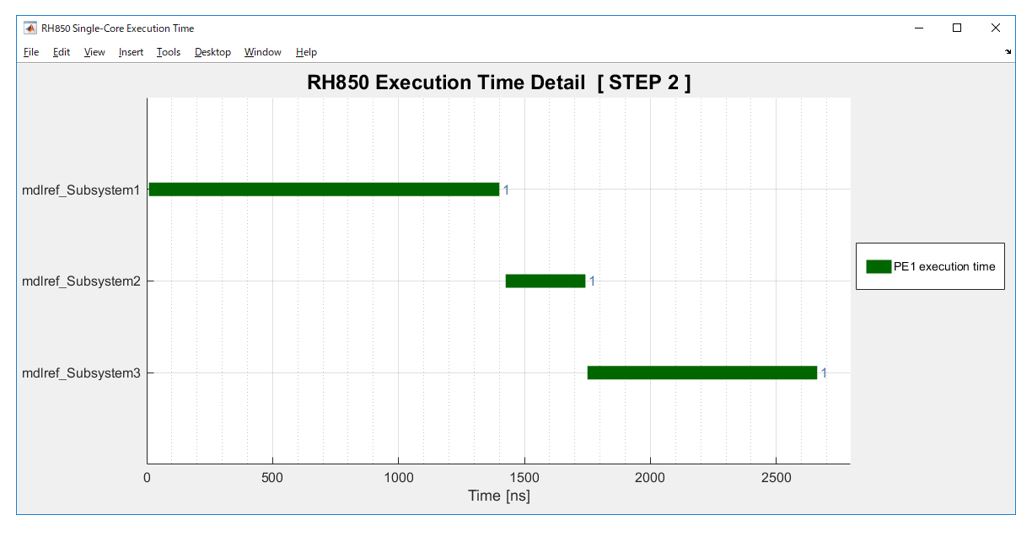

- シングルコアPILSとブロック性能解析

Embedded Target for RH850 Multicoreでは、PILSを行う際に、モデル内のサブシステムブロック単位での性能解析を行うことができます。これは他社にはない、Embedded Target for RH850特有の機能です。

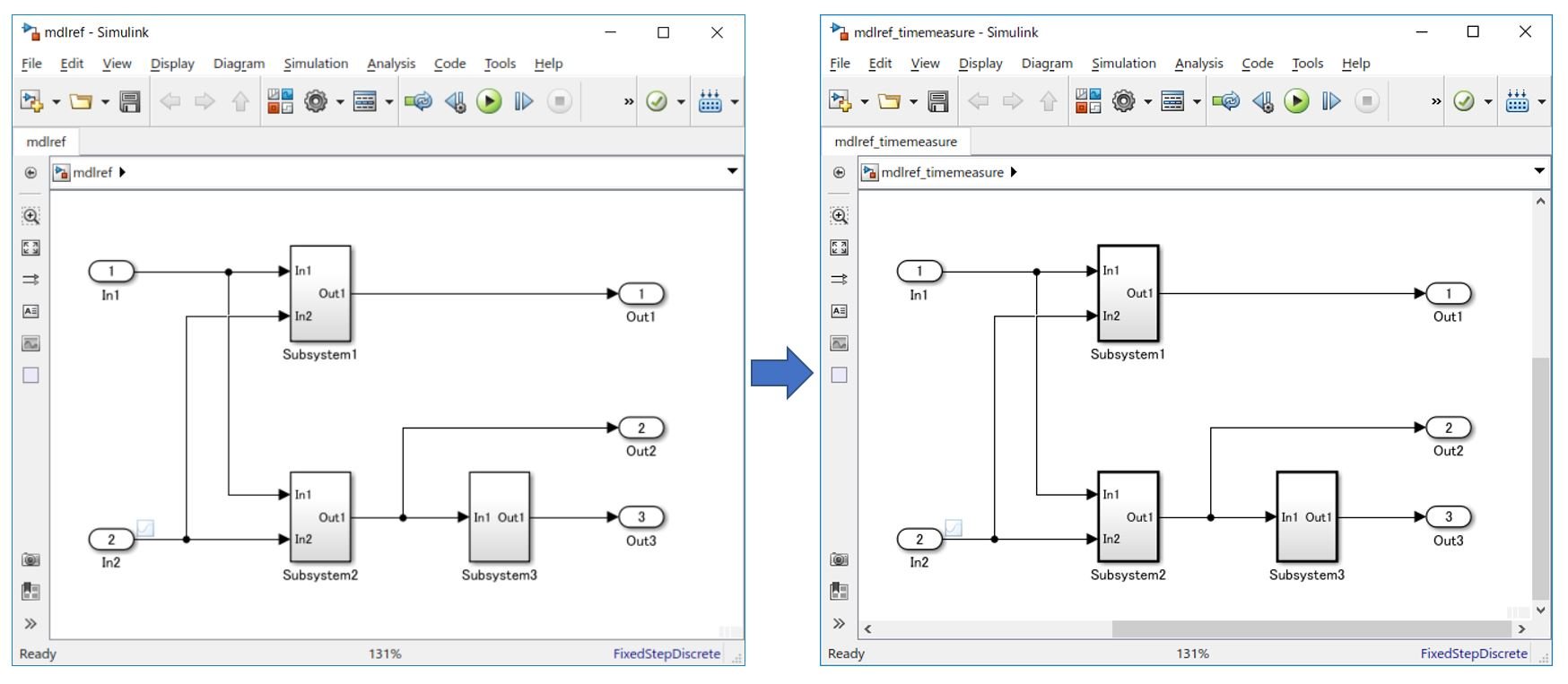

ブロック性能解析では、まずブロック性能解析用にモデルを変形します。専用のGUIで計測を行う対象のブロックを指定し、その後モデルの変形を行います。

上図はSimulinkのイメージです

ブロック性能解析用に変形したモデルからコードを生成し、PILSを行うことでブロック性能解析を行うことができます。結果はグラフで視覚的にブロック単位の実行時間を確認できます。

上記の説明はシングルコアの場合ですが、最新のRH850は多くがマルチコア化されており、ソフトウェアもマルチコアに対応する必要があります。マルチコアを使用する場合、シングルコアで動作させたソフトウェアをそのままマルチコアで動かしても、シングルコアと同じ動きになり、性能は向上しません。効率よくマルチコアを動かして性能を向上させるために、ソフトウェアをマルチコア向けに並列化する必要があります。並列化については次の章で説明します。

モデルから生成したコードをマルチコアMCU上で簡単に並列動作させるには?

マルチコアMCU上でソフトウェアを効率良く動作させるためには、複数のコアが処理を同時に実行できるように処理をなるべく均等に並列化する必要があります。また、ソフトウェアを並列化した後に、複数のコアが正しい順序で処理を実行させるための同期処理や、複数のコアで共有しているメモリなどの共有資源が複数のコアから同時にアクセスされないような排他制御を行う必要があります。これらを考慮してソフトウェアの並列化を行うのはとても難しい作業です。

苦労して並列化したソフトウェアを実際に動かしてみると、同期処理や排他制御のオーバーヘッドが大きく、期待した性能が出ないこともよくあります。

Embedded Target for RH850 Multicoreでは、モデルをマルチコア向けに並列化し、並列化したモデルからコードを生成することで、マルチコアで動作するコードを生成することができます。コード生成を行う際に、ブロックの実行順序を考慮してコア間の同期処理を挿入します。これにより、マルチコアで正しく動作するコードを生成することができます。

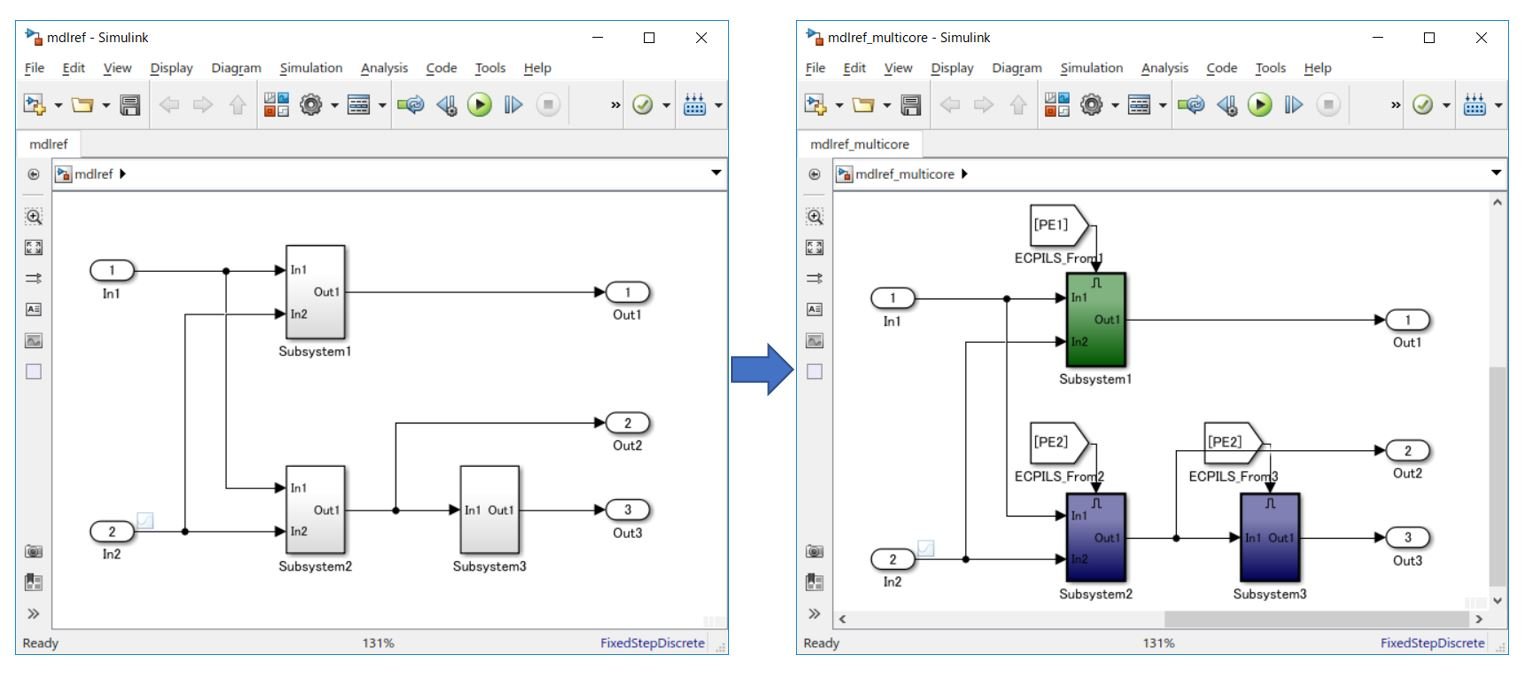

・ モデルをマルチコア向けに並列化する

ブロック性能解析の結果により各ブロックの処理時間がわかります。この情報を元に各ブロックをどのコアに割り付けるかを検討します。

コア割り付けは専用のGUIでブロックごとに割り付けるコアを指定し、その後モデルの変形を行います。これにより、モデルのマルチコア向け並列化が行えます。

上図はSimulinkのイメージです

※緑と青のブロックを異なるコアに割り付けています。

- マルチコアPILSによるBack-to-Backテスト

マルチコアでもシングルコアと同様に生成したコードを用いてPILSを行うことができます。PILSの実行結果とMILSの実行結果を比較してBack-to-Backテストを行うことができます。

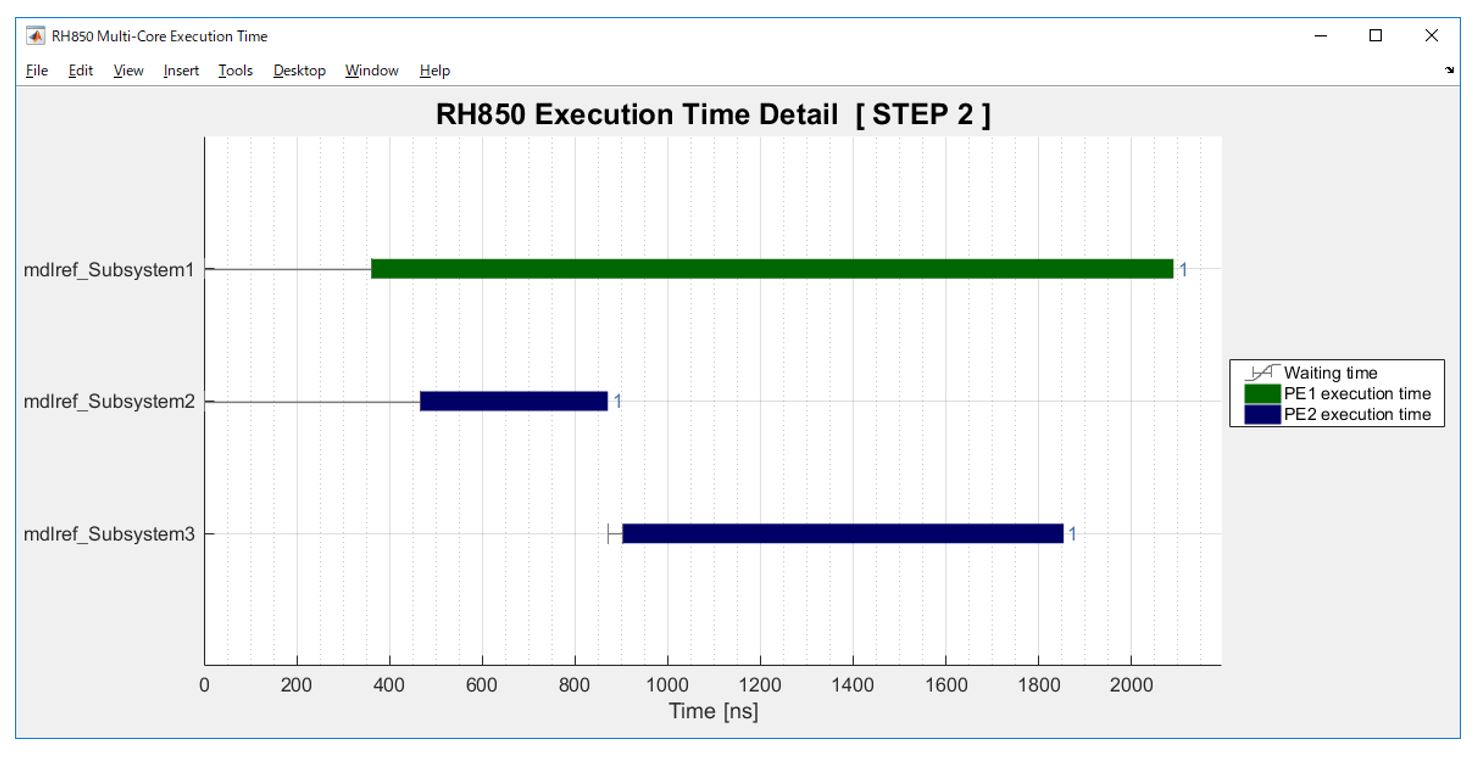

- マルチコアの性能解析と最適なマルチコア並列化の検証

マルチコアでもシングルコアと同様にブロック性能解析が行えます。結果はグラフで視覚的に確認可能です。上記の図のシングルコアの結果と比較して、トータルの実行時間が短くなるように、ブロック単位のコア割り付けを変更し、マルチコアPILSによる検証を繰り替えして、最適なマルチコア割り付けを検証します。

以上、シングルコア/マルチコアMCUに対応したモデルベース開発を説明しましたが、ルネサスではRH850マルチコア・モデルベース開発環境の整備をこれからも進めていきます。

Embedded Target for RH850 Multicoreの上位機能版であるEmbedded Target for RH850 Multicore + Multirate では、複数の制御周期を持つモデル(モデルベース開発ではマルチレートモデルと呼ばれています)にも対応しています。マルチレート対応機能についても記載しておりますので、ぜひこちらのEmbedded Target for RH850 Multicoreページもご覧ください。