-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

Clock Buffers, Fanout Buffers, and Clock Drivers

The Renesas clock buffer (clock driver) portfolio includes devices with up to 27 outputs. Differential outputs such as LVPECL, LVDS, HCSL, CML, HSTL, as well as selectable outputs, are supported for output frequencies up to 3.2GHz and single-ended LVCMOS outputs for frequencies up to 350MHz. Some buffers are available with mixed output signaling. The Renesas buffer portfolio has devices supporting supply voltages from 1.2V up to 5V and that are available in commercial and industrial temperature ranges. Fanout buffers and clock dividers are general-purpose clock building block devices that can be used in any number of applications. They are ideal for clock and signal distribution in a large variety of systems, from personal computers to consumer electronics or industrial systems, as well as high-performance networking and communications systems.

Standards

PCIe

JESD204B

Fanout Buffers (Clock Drivers)

Fanout buffers are a useful building block of many clock trees, providing signal buffering and multiple low-skew copies of the input signal. The clock buffer from a single input reduces loading on the preceding driver and provides an efficient clock distribution network. Single output clock buffers are useful for translating a clock from one signaling standard to another (e.g. LVCMOS-in to LVPECL-out). Some devices have an integrated crystal oscillator, requiring only a low cost external fundamental-mode quartz crystal. The integrated oscillator provides an extremely low phase noise reference clock to drive jitter-sensitive devices such as the clock inputs of PHYs. If the exact buffer configuration is not found in the extensive Renesas fanout buffer offerings, customers may consider devices in the Renesas clock divider or clock multiplexer portfolio that, when used in divide-by-1 mode or proper select mode, can also function as a fanout buffer.

Product Selection Table

Function |

Inputs (#) |

Outputs (#) |

Output Type |

Output Freq Range (MHz) |

Input Freq (MHz) |

Input Type |

Output Banks (#) |

Core Voltage (V) |

Output Voltage (V) |

Output Skew (ps) |

Additive Phase Jitter Typ RMS (fs) |

Divider Value |

Pkg. Dimensions (mm) |

Pkg. Type |

Temp. Range |

Lead Count (#) |

Prog. Interface |

Family Name |

105°C Max. Case Temp. |

Advanced Features |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Part Number | ||||||||||||||||||||||

| Low Skew 1 to 4 Clock Buffer | Buffer | 1 | 4 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 2.0 x 2.0 x 0.5, 4.9 x 3.9 x 1.5 | COL, SOIC | -40 to 85°C | 8 | 1.697 | |||||

| Low Skew 1 to 4 Clock Buffer | Buffer | 1 | 4 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 2.0 x 2.0 x 0.5, 4.9 x 3.9 x 1.5 | COL, SOIC | -40 to 85°C | 8 | 1.172 | |||||

| Programmable Fanout Buffer | Buffer, Multiplexer | 2 | 3 | HCSL, LVCMOS, LVDS, LVPECL | 1 - 350 | 1 - 350 | Crystal, HCSL, LVCMOS, LVDS, LVPECL | 3 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 35 | 4.0 x 4.0 x 0.9 | VFQFPN | -40 to 85°C | 24 | I2C, Pin select | 2.291 | |||||

| Programmable Fanout Buffer | Buffer, Multiplexer | 2 | 5 | HCSL, LVCMOS, LVDS, LVPECL | 1 - 350 | 1 - 350 | Crystal, HCSL, LVCMOS, LVDS, LVPECL | 5 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 35 | 4.0 x 4.0 x 0.9 | VFQFPN | -40 to 85°C | 24 | I2C, Pin select | 2.658 | |||||

| 1.8 V to 3.3 V 1:4 Crystal Input to LVCMOS Output High-Performance Clock Fanout Buffer with OE | Buffer | 1 | 4 | LVCMOS | 0 - 200 | 0 - 200 | Crystal, LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 50 | 2.5 x 2.5 x 0.5, 5.0 x 4.4 x 1.0 | COL, TSSOP | -40 to 105°C | 16 | 2.022 | |||||

| 1.8 V to 3.3 V 1:6 Crystal Input to LVCMOS Output High-Performance Clock Fanout Buffer with OE | Buffer | 1 | 6 | LVCMOS | 0 - 200 | 0 - 200 | Crystal, LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 50 | 2.5 x 2.5 x 0.5, 5.0 x 4.4 x 1.0 | COL, TSSOP | -40 to 105°C | 16 | 2.093 | |||||

| 1.8 V to 3.3 V 1:8 Crystal Input to LVCMOS Output High-Performance Clock Fanout Buffer with OE | Buffer | 1 | 8 | LVCMOS | 0 - 200 | 0 - 200 | Crystal, LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 50 | 3.0 x 3.0 x 1.0, 6.5 x 4.4 x 1.0 | TSSOP, VFQFPN | -40 to 105°C | 20 | 2.46 | |||||

| 1.8V to 3.3V 1:2 LVCMOS High Performance Clock Buffer | Buffer | 1 | 2 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 2.0 x 2.0 x 0.5, 3.1 x 4.4 x 1.0 | COL, TSSOP | -40 to 85°C, -40 to 105°C | 8 | 5PB | 0.9666 | ||||

| 1.8 V to 3.3 V 1:4 LVCMOS High Performance Clock Buffer | Buffer | 1 | 4 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 2.0 x 2.0 x 0.5, 2.0 x 2.0 x 0.75, 3.1 x 4.4 x 1.0 | COL, TSSOP | -40 to 85°C, -40 to 105°C, -40 to 125°C | 8 | 5PB | 1.259 | ||||

| 1.8 V to 3.3 V 1:6 LVCMOS High Performance Clock Buffer | Buffer | 1 | 6 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 2.5 x 2.5 x 0.5, 5.0 x 4.4 x 1.0 | COL, TSSOP | -40 to 85°C, -40 to 105°C | 14, 16 | 5PB | 1.683 | ||||

| 1.8 V to 3.3 V 1:8 LVCMOS High Performance Clock Buffer | Buffer | 1 | 8 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 2.5 x 2.5 x 0.5, 5.0 x 4.4 x 1.0 | COL, TSSOP | -40 to 85°C, -40 to 105°C | 16 | 5PB | 1.753 | ||||

| 1.8 V to 3.3 V 1:10 LVCMOS High Performance Clock Buffer | Buffer | 1 | 10 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS | 1 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 65 | 35 | 3.0 x 3.0 x 1.0, 6.5 x 4.4 x 1.0 | TSSOP, VFQFPN | -40 to 85°C, -40 to 105°C | 20 | 5PB | 2.828 | ||||

| 1.8 V 1:3 TCXO / LVCMOS High-Performance Clock Buffer | Buffer | 1 | 3 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS, Sine Wave | 1 | 1.8 | 1.8 | 65 | 50 | 2.0 x 2.0 x 0.75 | DFN | -40 to 105°C | 10 | 5PB | 0.9666 | ||||

| 1.8 V 1:4 TCXO / LVCMOS High-Performance Clock Buffer | Buffer | 1 | 4 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS, Sine Wave | 1 | 1.8 | 1.8 | 65 | 50 | 2.5 x 2.5 x 0.5 | COL | -40 to 105°C | 16 | 5PB | 1.259 | ||||

| 1.8 V 1:6 TCXO / LVCMOS High-Performance Clock Buffer | Buffer | 1 | 6 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS, Sine Wave | 1 | 1.8 | 1.8 | 65 | 50 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 105°C | 20 | 5PB | 1.995 | ||||

| 2.5 V to 3.3 V 1:3 TCXO / LVCMOS High-Performance Clock Buffer | Buffer | 1 | 3 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS, Sine Wave | 1 | 2.5, 3.3 | 2.5, 3.3 | 65 | 50 | 2.0 x 2.0 x 0.75 | DFN | -40 to 105°C | 10 | 5PB | 0.9666 | ||||

| 2.5 V to 3.3 V 1:4 TCXO / LVCMOS High-Performance Clock Buffer | Buffer | 1 | 4 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS, Sine Wave | 1 | 2.5, 3.3 | 2.5, 3.3 | 65 | 50 | 2.5 x 2.5 x 0.5 | COL | -40 to 105°C | 16 | 5PB | 1.259 | ||||

| 2.5 V to 3.3 V 1:6 TCXO / LVCMOS High-Performance Clock Buffer | Buffer | 1 | 6 | LVCMOS | 0 - 200 | 0 - 200 | LVCMOS, Sine Wave | 1 | 2.5, 3.3 | 2.5, 3.3 | 65 | 50 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 105°C | 20 | 5PB | 1.995 | ||||

| Low Skew,1-to-6,Differential-to-2.5V,3.3V LVPECL/ECL Fanout Buffer | Buffer | 2 | 6 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5, 3.3 | 2.5, 3.3 | 50 | 100 | 6.5 x 4.4 x 1.0 | TSSOP | -40 to 85°C | 20 | 5.222 | |||||

| Low Skew,1-to-2,Differential-to-2.5V,3.3V LVPECL/ECL Fanout Buffer | Buffer | 1 | 2 | ECL, LVPECL | 0 - 2500 | 0 - 2500 | CML, LVDS, LVPECL, SSTL | 1 | 2.5, 3.3 | 2.5, 3.3 | 5 | 26 | 3.0 x 3.0 x 0.97, 4.9 x 3.9 x 1.5 | SOIC, TSSOP | -40 to 85°C | 8 | 3.083 | |||||

| Low Skew,1-to-5 Differential-to-2.5V,3.3V LVPECL/ECL Fanout Buffer | Buffer, Multiplexer | 2 | 5 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL, SSTL | 1 | 2.5, 3.3 | 2.5, 3.3 | 55 | 100 | 6.5 x 4.4 x 1.0 | TSSOP | -40 to 85°C | 20 | 7.093 | |||||

| Low Skew, 1-to-10 Differential-to-2.5V, 3.3V LVPECL / ECL Fanout Buffer | Buffer, Multiplexer | 2 | 10 | LVPECL | 0 - 2500 | 0 - 2500 | LVDS, LVPECL, SSTL | 1 | 2.5, 3.3 | 2.5, 3.3 | 50 | 30 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | 3.859 | |||||

| Low Skew,1-to-12,Differential-to-3.3V,2.5V LVPECL Fanout Buffer | Buffer | 1 | 12 | LVPECL | 0 - 1500 | 0 - 1500 | CML, LVPECL, SSTL | 1 | 2.5, 3.3 | 2.5, 3.3 | 50 | 60 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | 26.3 | |||||

| Crystal or Differential to LVCMOS/ LVTTL Clock Buffer | Buffer, Multiplexer | 3 | 10 | LVCMOS | 0 - 200 | 0 - 200 | Crystal, HCSL, LVCMOS, LVDS, LVPECL | 1 | 2.5, 3.3 | 1.5, 1.8, 2.5, 3.3 | 63 | 22 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | 8L30 | |||||

| Crystal or Differential to LVCMOS/ LVTTL Clock Buffer | Buffer, Multiplexer | 2 | 5 | LVCMOS | 0 - 200 | 0 - 200 | Crystal, HCSL, LVCMOS, LVDS, LVPECL | 2 | 2.5, 3.3 | 1.5, 1.8, 2.5, 3.3 | 30 | 30 | 4.0 x 4.0 x 0.9 | VFQFPN | -40 to 85°C | 24 | 8L30 | 1.767 | ||||

| Crystal or Differential to LVCMOS/ LVTTL Clock Buffer | Buffer, Multiplexer | 3 | 10 | LVCMOS | 0 - 200 | 0 - 200 | Crystal, HCSL, LVCMOS, LVDS, LVPECL | 2 | 2.5, 3.3 | 1.5, 1.8, 2.5, 3.3 | 30 | 30 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | 8L30 | 2.234 | ||||

| 1:2 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer | 1 | 2 | LVDS | 0 - 1200 | 0 - 1200 | CML, LVDS, LVPECL | 1 | 1.8 | 1.8, 2.5 | 20 | 42 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8P34S | 6.857 | ||||

| 1:6 LVDS Output 1.8V Fanout Buffer | Buffer | 1 | 6 | LVDS | 0 - 1200 | 0 - 1200 | CML, LVDS, LVPECL | 1 | 1.8 | 1.8, 2.5 | 20 | 39 | 4.0 x 4.0 x 1.0 | VFQFPN | -40 to 85°C | 20 | 8P34S | 6.757 | ||||

| 2:4 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer, Multiplexer | 2 | 4 | LVDS | 0 - 1200 | 0 - 1200 | CML, LVDS, LVPECL | 1 | 1.8 | 1.8, 2.5 | 14 | 42 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8P34S | 5.972 | ||||

| 2:8 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer, Multiplexer | 2 | 8 | LVDS | 0 - 1200 | 0 - 1200 | CML, LVDS, LVPECL | 1 | 1.8 | 1.8, 2.5 | 20 | 41 | 5.0 x 5.0 x 0.8 | VFQFPN | -40 to 85°C | 28 | 8P34S | 6.757 | ||||

| 2:12 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer, Multiplexer | 2 | 12 | LVDS | 0 - 1200 | 0 - 1200 | CML, LVDS, LVPECL | 1 | 1.8 | 1.8, 2.5 | 12 | 73 | 6.0 x 6.0 x 0.9 | VFQFPN | -40 to 85°C | 40 | 8P34S | |||||

| Dual 1:2 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer | 2 | 4 | LVDS | 0 - 2000 | 0 - 2000 | LVCMOS, LVDS, LVPECL | 2 | 1.8 | 1.8, 2.5 | 30 | 45 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C (Tc ≤ 105°C) | 16 | 8P34S | Yes | Dual Buffer, Output Amplitude Control | 6.857 | ||

| Dual 1:4 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer | 2 | 8 | LVDS | 0 - 2000 | 0 - 2000 | LVCMOS, LVDS, LVPECL | 2 | 1.8 | 1.8, 2.5 | 30 | 45 | 5.0 x 5.0 x 0.8 | VFQFPN | -40 to 85°C (Tc ≤ 105°C) | 28 | 8P34S | Yes | Dual Buffer, Output Amplitude Control | 6.757 | ||

| Dual 1:6 LVDS Output 1.8V / 2.5V Fanout Buffer | Buffer | 2 | 12 | LVDS | 0 - 2000 | 0 - 2000 | LVCMOS, LVDS, LVPECL | 2 | 1.8 | 1.8, 2.5 | 40 | 45 | 3.59 x 3.04 x 0.6 | WLCSP | -40 to 85°C (Tc ≤ 105°C) | 48 | 8P34S | Yes | Dual Buffer, Output Amplitude Control | |||

| Dual 1:6 LVDS Output 1.8V / 2.5V Fanout Buffer | 1.8, 2.5 | 6.0 x 6.0 x 0.9 | VFQFPN | -40 to 85°C | 40 | 7.906 | ||||||||||||||||

| Dual 1:8 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | Buffer | 2 | 16 | LVDS | 0 - 2000 | 0 - 2000 | LVCMOS, LVDS, LVPECL | 2 | 1.8 | 1.8, 2.5 | 40 | 45 | 7.0 x 7.0 x 0.9 | VFQFPN | -40 to 85°C (Tc ≤ 105°C) | 48 | 8P34S | Yes | Dual Buffer, Output Amplitude Control | 8.503 | ||

| Low Additive Jitter 2:8 Buffer with Universal Differential Outputs | Buffer | 2 | 8 | CML, HCSL, LVDS, LVPECL | 0.000001 - 1000 | 0.000001 - 1000 | CSL, LVCMOS, LVDS, LVHSTL, LVPECL | 2 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 100 | 70 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | Pin select | 8P39 | 5.29 | |||

| Low Additive Jitter 2:8 Buffer with CMOS / Differential Outputs | Buffer, Divider, Multiplexer | 2 | 8 | LVCMOS, LVDS, LVPECL | CSL, LVCMOS, LVDS, LVHSTL, LVPECL | 2 | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 100 | 80 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | Pin select | 8P79 | 6.985 | |||||

| Programmable Low Additive Jitter 2:8 Buffer with Dividers and Universal Outputs | Buffer, Divider | 2 | 8 | CML, HCSL, LVDS, LVPECL | 0.000001 - 700 | 0.000001 - 700 | LVCMOS, LVDS, LVHSTL, LVPECL | 2 | 1.8, 2.5, 3.3 | 1.5, 1.8, 2.5, 3.3 | 100 | 60 | 2, 511 | 5.0 x 5.0 x 0.9 | VFQFPN | -40 to 85°C | 32 | I2C | 8P79 | 4.404 | ||

| 2:4, LVDS Output Fanout Buffer, 2.5V | Buffer, Multiplexer | 2 | 4 | LVDS | 0 - 2000 | 0 - 2000 | LVDS, LVPECL | 1 | 2.5 | 2.5 | 20 | 95 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8SLVD | 4.227 | ||||

| 2:4, LVDS Output Fanout Buffer, 3.3 V | Buffer, Multiplexer | 2 | 4 | LVDS | 0 - 2000 | 0 - 2000 | LVDS, LVPECL | 1 | 3.3 | 3.3 | 20 | 95 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8SLVD | 4.227 | ||||

| 1:8, LVDS Output Fanout Buffer | Buffer, Multiplexer | 2 | 8 | LVDS | 0 - 2000 | 0 - 2000 | LVDS, LVPECL | 1 | 3.3 | 3.3 | 20 | 82 | 5.0 x 5.0 x 0.8 | VFQFPN | -40 to 85°C | 28 | 8SLVD | |||||

| 1:12, LVDS Output Fanout Buffer | Buffer, Multiplexer | 2 | 12 | LVDS | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5 | 2.5 | 45 | 65 | 6.0 x 6.0 x 0.9 | VFQFPN | -40 to 85°C | 40 | 8SLVD | 5.113 | ||||

| Dual 1:4, LVDS Output Fanout Buffer | Buffer | 2 | 8 | LVDS | 0 - 2000 | 0 - 2000 | LVDS, LVPECL | 2 | 2.5 | 2.5 | 35 | 105 | 5.0 x 5.0 x 0.8 | VFQFPN | -40 to 85°C | 28 | 8SLVD | Dual Buffer | 4.363 | |||

| 1:2,LVPECL Output Fanout Buffer | Buffer | 1 | 2 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5, 3.3 | 2.5, 3.3 | 15 | 36 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8SLVP | 3.295 | ||||

| Low Phase Noise,1-to-4, 3.3V, 2.5V LVPECL Output Fanout Buffer | Buffer | 1 | 4 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5, 3.3 | 2.5, 3.3 | 15 | 32 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8SLVP | 3.859 | ||||

| 2:4 LVPECL Output Fanout Buffer | Buffer, Multiplexer | 2 | 4 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5, 3.3 | 2.5, 3.3 | 64 | 32 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C (Tc ≤ 105°C) | 16 | 8SLVP | Yes | 3.613 | |||

| 2:8,LVPECL Output Fanout Buffer | Buffer, Multiplexer | 2 | 8 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5, 3.3 | 2.5, 3.3 | 64 | 31.1 | 5.0 x 5.0 x 0.8 | VFQFPN | -40 to 85°C | 28 | 8SLVP | 5.249 | ||||

| 2:12,3.3V,2.5V LVPECL Fanout Buffer | Buffer, Multiplexer | 2 | 12 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 1 | 2.5, 3.3 | 2.5, 3.3 | 15 | 45 | 6.0 x 6.0 x 0.9 | VFQFPN | -40 to 85°C | 40 | 8SLVP | 12.26 | ||||

| Dual 1:2, 3.3V, 2.5V LVPECL Output Fanout Buffer | Buffer | 2 | 4 | LVPECL | 0 - 2000 | 0 - 2000 | CML, LVDS, LVPECL | 2 | 2.5, 3.3 | 2.5, 3.3 | 15 | 31 | 3.0 x 3.0 x 1.0 | VFQFPN | -40 to 85°C | 16 | 8SLVP | Dual Buffer | 3.763 |

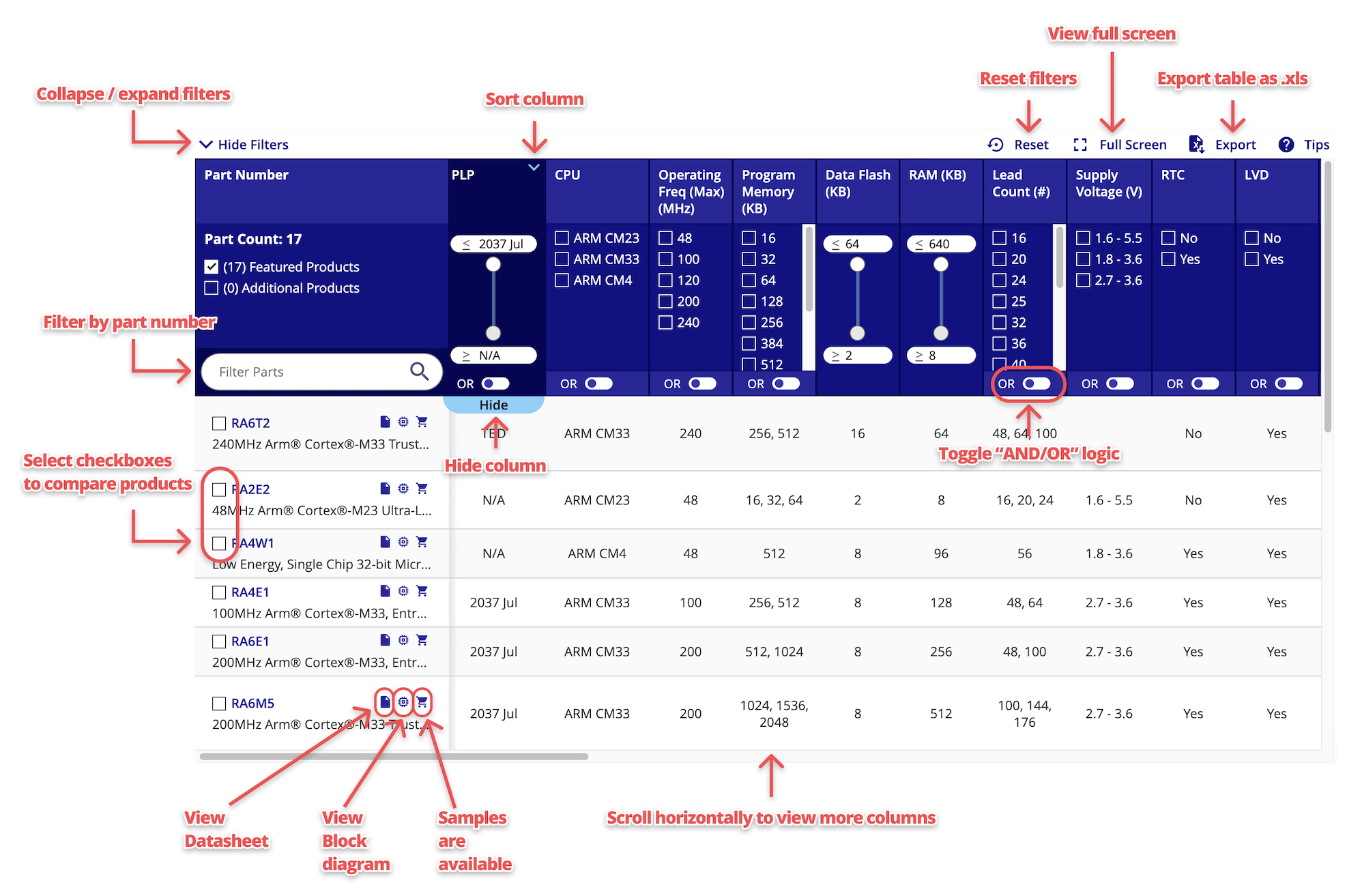

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

Videos & Training

This video provides an overview of the LVCMOS High Performance Clock Buffer Family, highlighting their key features and capabilities.