概要

説明

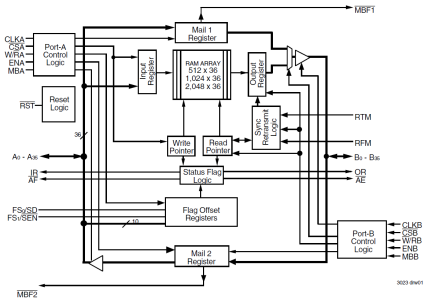

The 723641 is a 1K x 36 Sync FIFO memory that supports clock frequencies up to 67 MHz and has read access times as fast as 12ns. The FIFO memory has retransmit capability, which allows previously read data to be accessed again. Communication between each port may take place with two 36-bit mailbox registers. All data transfers through a port are gated to the LOW-to-HIGH transition of a continuous port clock by enable signals.

特長

- Free-running CLKA and CLKB can be asynchronous or coincident

- Clocked FIFO buffering data from Port A to Port B

- Synchronous read retransmit capability

- Mailbox register in each direction

- Programmable Almost-Full and Almost-Empty flags

- Microprocessor interface control logic

- Available in 132-pin PQFP and 120-pin TQFP packages

- Industrial temperature range (–40C to +85C) is available

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター