AD/ADAS向けSoCのAI性能計最適化について

1. 背景

近年、深層学習(ディープラーニング)による人工知能 (AI) の技術の進歩により、例えば自動翻訳の精度の向上や、消費者の好みに合ったおすすめの提案など、私たちの生活に直接役に立つ場面が増えてきました。2023年現在では、分野によっては製品やサービスへのAIの適用が必須とも言える状況になってきており、そのひとつとして、自動車の自動運転(AD)や先進運転支援(ADAS)があります。

深層ニューラルネットワーク(DNN)に代表される近年のAIモデルの処理には大規模な並列演算が必要となるため、PC上の開発では汎用的に並列演算が可能なGPUがよく使用されています。一方、ADやADAS向けのSoCでは、DNN処理を低消費電力・高性能で実現する専用回路(以下、アクセラレータと表記)を搭載することが多くなってきました。しかし、搭載するアクセラレータが実際に使用したいDNNで十分な性能を出せるかどうかを、SoCの開発の早い段階で確認するのは、一般的に簡単ではありません。性能比較の指標としてはアクセラレータの設計上の最大演算性能を表すTOPS (Tera Operations Per Second)値や、前記を動作時の消費電力で割ったTOPS/W値がしばしば使用されますが、アクセラレータは特定の処理を高速に実行するように専用設計(*1)するため、TOPS値は十分でも、実際に使用したいDNNでは効率的な処理ができない演算の存在やデータ転送帯域の不足などにより、十分な性能を出せないことが考えられます。また、アクセラレータの電力の増加により、SoC全体としての消費電力が許容範囲を超えることも考えられます。

(*1) 専用設計:汎用的なGPUをアクセラレータとして使用することも可能ですが、対象を特定の処理に絞ってハードウェア化することにより、少ない回路規模と電力で高い処理性能を得られます。一例としてRenesasの車載向けSoCであるR-Car V3H、R-Car V3MやR-Car V4Hに搭載のアクセラレータは、DNNの中でも畳み込み演算を特徴抽出に使用する畳み込みニューラルネットワーク(CNN)の処理に適した構造となっています。

SoCの開発が進めば進むほど、性能不足や消費電力過剰などの理由で設計変更を行う場合の難易度は一般的に上昇し、SoCの開発日程や開発費用への影響も大きくなります。このため、搭載するアクセラレータが顧客製品で実際に使用したいDNNで十分な性能を出せるか、消費電力が許容範囲内に収まっているかをSoCの開発の早い段階で確認することが、車載AI機器向けSoCを開発する上で喫緊の課題となっています。

2. 一般的なAD/ADAS向けAI開発の流れ

上記の課題への取り組みの説明に入る前に、AD/ADASにおけるAI開発の流れを簡単に説明します。

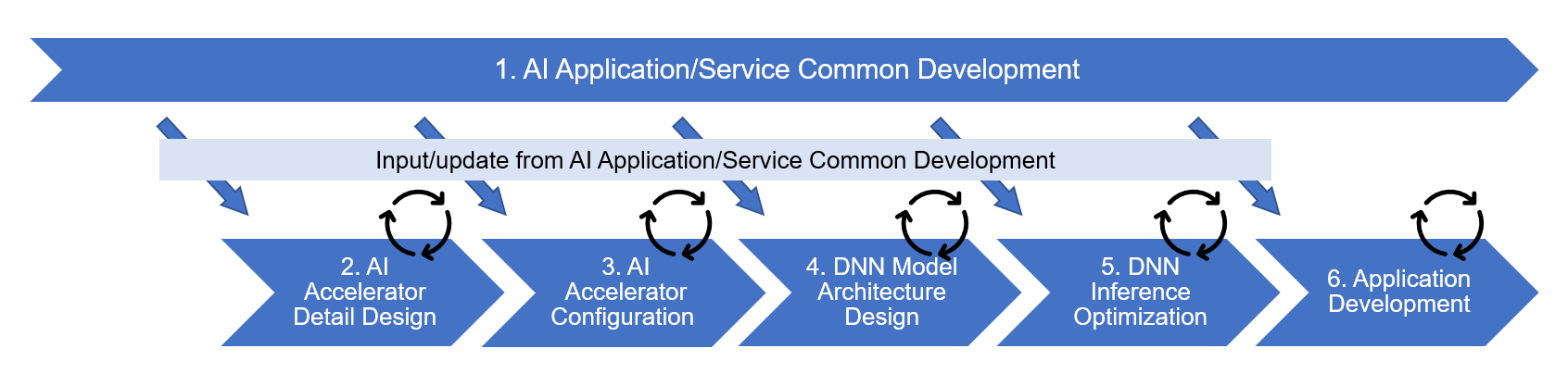

以下の図1に、ソフトウェアを中心として一部SoCの開発を含めたAD/ADASにおけるAI開発の流れの例を示します。

図1では開発全体を6つのフェーズに区分しており、フェーズ2と3はSoCの回路設計、それ以外のフェーズ1及び4-6はソフトウェア開発となります。また、各フェーズにおける作業の概要は以下の通りです。

1のAI Application/Service Common Developmentでは、市場ニーズや技術動向に対応して、継続的にPCやクラウド環境を活用したAD/ADAS向けのAIアプリケーションやサービスの開発を行います。

2のAI Accelerator Detail Designでは、アクセラレータのハードウェアを構成する演算ユニットや内蔵メモリ、データ転送ユニットなどの部品の設計を行います。

3のAI Accelerator Configurationでは、2で設計した部品を組み合わせ、面積、電力、性能などのトレードオフを最適化しながら、それぞれの設計目標を達成できるようにSoCに搭載するアクセラレータの構成を決定します。

4のDNN Model Architecture Designでは、3で決定されたアクセラレータの構成を使用し、顧客製品で利用を想定する各DNNのネットワークの構造を最適化します。

5のDNN Interface Optimizationでは、4で構造を最適化した各ネットワークに対して、アクセラレータ向けのコード生成、精度や処理時間の詳細な評価とコードやモデルデータの最適化を行います。

6のApplication Developmentでは、5で最適化されたコードとモデルデータを用いて実装したAI処理部分を実際の自動運転などの処理を行うアプリケーションに組み込み、アプリケーション側の実装と評価を行います。

3. Renesasの取り組み

前節で示したAD/ADASにおけるAI開発の流れにおいて、実際に使用したいDNNが搭載するアクセラレータで十分な性能を出せるかどうかの判断は、基本的にアクセラレータの構成を決定する3のAI Accelerator Configurationのフェーズで行う必要があります。

従来、この段階での判断は、類似のアクセラレータを搭載する既存のSoCを使用して実施したベンチマークの結果から推定することで行ってきましたが、機能の追加や変更により既存のSoCと仕様の異なる部分についてはベンチマーク結果を得られないため、確度の高い推定に基づき、設計目標を達成できるかどうかの判断ができない課題がありました。

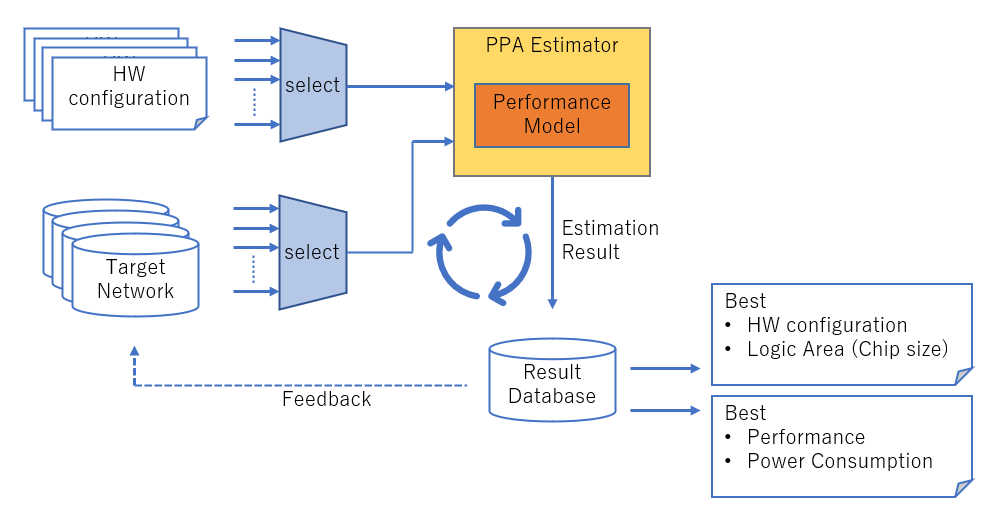

今回Renesasでは、既存のSoCによるベンチマークの代わりにPPA Estimator (PPAはPerformance, Power, Areaの頭文字)を用いることにより、この課題への対応を図りました。PPA Estimatorでは、アクセラレータの各部品の設計を反映して作成した性能と電力の計算モデルを使用することにより、アクセラレータの構成確定前の時点での性能と消費電力の見積もりを可能とします。具体的には、可能なアクセラレータの構成(処理ユニットの個数や内蔵メモリの容量といったアクセラレータの変更可能なパラメータの組み合わせ)の中から評価対象とするものを列挙しておき、その中からひとつを選んで、評価対象のDNNのひとつと合わせてPPA Estimatorに入力し、所要時間と消費電力を求めます。これを必要な評価対象のアクセラレータの構成及びDNNの個数分繰り返してデータを取得し、最適なアクセラレータの構成を求めます。これにより、単に特定のアクセラレータの構成とDNNの組み合わせで十分な性能が出るかを判断するだけではなく、広くデータを収集してその中から最適なアクセラレータの構成を選択することが可能となります。

また、Renesasでは3のAI Accelerator Configurationのフェーズをより効果的なものとするため、対象のDNNのネットワークモデルにPPA Estimatorの実行結果から得られた情報をフィードバックすることで並行してソフト側の改善も図るハード・ソフト協調設計(co-design)を行います。これらを含めたAI Accelerator Configurationのフェーズの作業フローを以下の図2に示します。

Renesasでは、2023年よりAI処理に向けたアクセラレータを搭載する一部のAD/ADAS向けSoCの開発へのPPA Estimatorの適用を開始しており、今後は順次適用対象を拡大していく予定です。RenesasはPPA Estimatorによる高精度性能見積を用いて最適構成を探索し、高性能・低消費電力な車載 AI アクセラレータを開発していきます。

Renesasの車載AI向けSoCの現在の最新製品については以下のリンクで紹介しておりますので、ぜひご覧ください。

R-Car-V4H - 自動運転レベル2+ / レベル3向け、超低消費電力でクラス最高のディープラーニングを実現する車載用SoC | Renesas