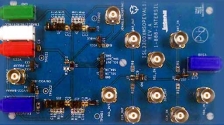

I2C Bus Buffer with Rise Time Accelerators and Hot Swap Capability Evaluation Board

The ISL33001MSOPEVAL1Z evaluation board is designed to provide a quick and easy method for evaluating the ISL33001 two-channel bus buffer with rise time accelerators...