Overview

Description

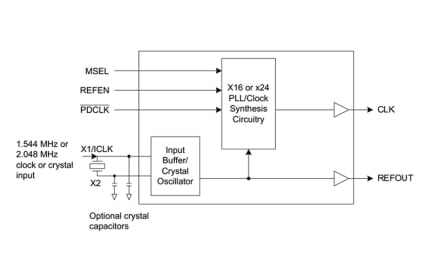

The 548-05 is a low-cost, low-jitter, high-performance clock synthesizer designed to produce x16 and x24 clocks from T1 and E1 frequencies. Using Renesas’ patented analog/digital Phase-Locked Loop (PLL) techniques, the device uses a crystal or clock input to synthesize popular communications frequencies. Power down modes allow the chip to turn off completely, or the PLL and clock output to be turned off separately.

Features

- Packaged in 16-pin TSSOP

- Available in Pb (lead) free package

- Ideal for telecom/datacom chips

- Replaces oscillators

- 3.3 V or 5 V operation

- Uses a crystal or clock input

- Produces 24.704, 37.056, 32.768, or 49.152 MHz

- Includes Power-down features

- Advanced, low-power, sub-micron CMOS process

- See also the MK2049-34 for generating

- Industrial temperature range available

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: