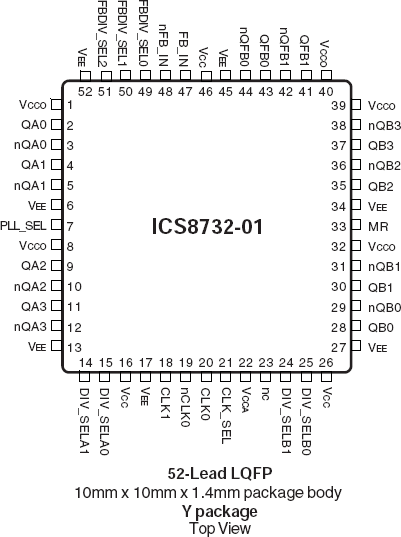

Package Information

| Lead Count (#) | 52 |

| Pkg. Type | TQFP |

| Pkg. Code | PPG52 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.4 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN | NLR |

| HTSUS | 8542390001 |

Product Attributes

| Pkg. Type | TQFP |

| Lead Count (#) | 52 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range | 0 to 70°C |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 50 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 0 - 200 |

| Input Type | HCSL, HSTL, LVCMOS, LVDS, LVPECL, SSTL |

| Inputs (#) | 2 |

| Length (mm) | 10 |

| MOQ | 1000 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 0 - 350 |

| Output Skew (ps) | 150 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 8 |

| Package Area (mm²) | 100.0 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.4 |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1.4 |

| Width (mm) | 10 |

Description

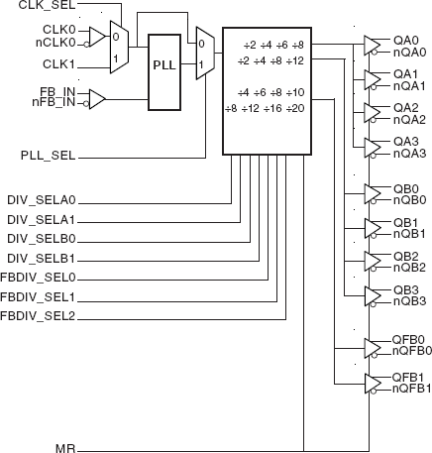

The 8732-01 is a low voltage, low skew, 3.3V LVPECL Clock Generator. The 8732-01 has two selectable clock inputs. The CLK0, nCLK0 pair can accept most standard differential input levels. The single ended clock input accepts LVCMOS or LVTTL input levels. The 8732-01 has a fully integrated PLL along with frequency configurable outputs. An external feedbackinput and outputs regenerate clocks with "zero delay". The 8732-01 has multiple divide select pins for each bank of outputs along with 3 independent feedback divide select pins allowing the 8732-01 to function both as a frequency multiplier and divider. The PLL_SEL input can be usedto bypass the PLL for test and system debug purposes.In bypass mode, the input clock is routed around the PLLand into the internal output dividers.