-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

Radio Synchronizers & JESD204B/C Clock Jitter Attenuators

Radio synchronizers and JESD204B/C clock jitter attenuators offer industry-leading phase noise for best 4G/5G radio EVM performance, excellent close-in phase noise for enhanced Common Public Radio Interface (eCPRI) and CPRI applications, and high fanout for high-density radios.

Single-chip radio synchronization devices integrate digital PLLs (DPLLs) with a high-performance RF PLL and support PTP (Precision Timing Protocol, IEEE 1588), synchronous Ethernet, 1PPS input and output signals, and a tight phase alignment.

These devices remove virtually all noise from an input reference clock, making them suitable for the data converter reference clock generation and synchronization.

Product Selection Table

Outputs (#) |

Inputs (#) |

Input Freq (MHz) |

DPLL Channels (#) |

JESD204B/C Compliant |

Output Freq Range (MHz) |

Frequency Plan |

Output Skew (ps) |

Adjustable Phase |

Noise Floor (dBc/Hz) |

Phase Noise Supports GSM |

Output Type |

Synthesis Mode |

Input Ref. Divider Resolution (bits) |

Feedback Divider Resolution (bits) |

Output Divider Resolution (bits) |

Supply Voltage (V) |

Input Redundancy |

Advanced Features |

Pkg. Type |

Lead Count (#) |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Part Number | ||||||||||||||||||||||

| Radio Synchronizer | 16 | 2 | 0.000001 - 1000 | 2 | Yes | 0.000001 - 1000 | 2500 / Output_Divider, 2949.12 / Output_Divider, 3670-3868 / Output_Divider | 74 | Yes | -165 | Yes | LVCMOS, LVDS, LVPECL | Fractional, Integer | 3 | 32 | 7 | 3.3, 2.5, 1.8 | Digital holdover, Hitless switch, Input Monitor, Phase-slope limiting | 1PPS, DCO, IEEE 1588, JESD204B, JESD204C, T-BC, T-TSC Class C, eEEC | VFQFPN | 88 | 26.95 |

| JESD204B/C Clock Jitter Attenuator | 16 | 2 | 0.00375 - 2000 | 0 | Yes | 0.192 - 6000 | 3932.16 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 15 | 15 | 7 | 3.3, 2.5, 1.8 | Auto-switch, Holdover, Input Monitor, Manual input switch | Holdover, Input Switching, JESD204B | VFQFPN | 76 | |

| Clock Jitter Attenuator | 10 | 2 | 0.008 - 307.2 | 0 | No | 15.36 - 2949.12 | 2457.6 / Output_Divider, 2500 / Output_Divider, 2949.12 / Output_Divider | 41 | Yes | -161 | Yes | LVDS, LVPECL | Integer | 15 | 15 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 81 | |

| Clock Jitter Attenuator | 11 | 2 | 0.008 - 307.2 | 0 | No | 15.36 - 2949.12 | 2457.6 / Output_Divider, 2500 / Output_Divider, 2949.12 / Output_Divider | 28 | Yes | -158.7 | Yes | LVDS, LVPECL | Integer | 15 | 15 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, Phase Delay, Programmable Clock | CABGA | 81 | |

| JESD204B/C Clock Jitter Attenuator | 12 | 2 | 0.008 - 250 | 0 | No | 15.625 - 2500 | 2400 / Output_Divider, 2500 / Output_Divider | 70 | Yes | -161 | Yes | LVDS, LVPECL | Fractional, Integer | 15 | 15 | 8 | 3.3 | Auto-switch, Input Monitor, Manual switch | Holdover, Input Switching, Phase Delay | CABGA | 81 | 23.07 |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 30.72 - 500 | 0 | Yes | 20.48 - 1474.56 | 2949.12 / Output_Divider | 37 | Yes | -161 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 1.92 - 2000 | 0 | Yes | 18.432 - 2949.12 | 2949.12 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 1.92 - 2000 | 0 | Yes | 12.288 - 1966.08 | 1966.08 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 1.92 - 2000 | 0 | Yes | 15.36 - 2457.6 | 2457.6 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 1.92 - 2000 | 0 | Yes | 18.432 - 2949.12 | 2949.12 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 1.92 - 2000 | 0 | Yes | 18.432 - 2949.12 | 2949.12 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 15 | 2 | 1.92 - 2000 | 0 | Yes | 12.288 - 2457.6 | 2457.6 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | VFQFPN | 88 | |

| JESD204B/C Clock Jitter Attenuator | 18 | 4 | 30.72 - 2000 | 0 | Yes | 18.432 - 3686.4 | 3686.4 / Output_Divider | 100 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | CABGA | 100 | |

| JESD204B/C Clock Jitter Attenuator | 15 | 2 | 1.92 - 2000 | 0 | Yes | 18.432 - 2949.12 | 2949.12 / Output_Divider | 0 | Yes | -160 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | VFQFPN | 88 | 14.32 |

| JESD204B/C Clock Jitter Attenuator | 15 | 2 | 30.72 - 2000 | 0 | Yes | 19.6608 - 3932.16 | 3932.16 / Output_Divider | 100 | Yes | -160.2 | Yes | LVDS, LVPECL | Integer | 12 | 12 | 8 | 3.3 | Auto-switch, Holdover, Input Monitor, Manual switch and more... |

Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | VFQFPN | 88 | |

| Radio Access Network Equipment Synchronizer - Six Channels | 24 | 10 | 0.001 - 1000 | 6 | Yes | 0.0000005 - 1000 | 50 | Yes | -158 | No | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | Fractional, Integer | 4 | 48 | 32 | 3.3, 2.5, 1.8 | Digital holdover, Hitless switch, Input Monitor, Phase-slope limiting | 1PPS, DCO, IEEE 1588, JESD204B, JESD204C, PWM Encoder/Decoder and more... |

VFQFPN | 72 |

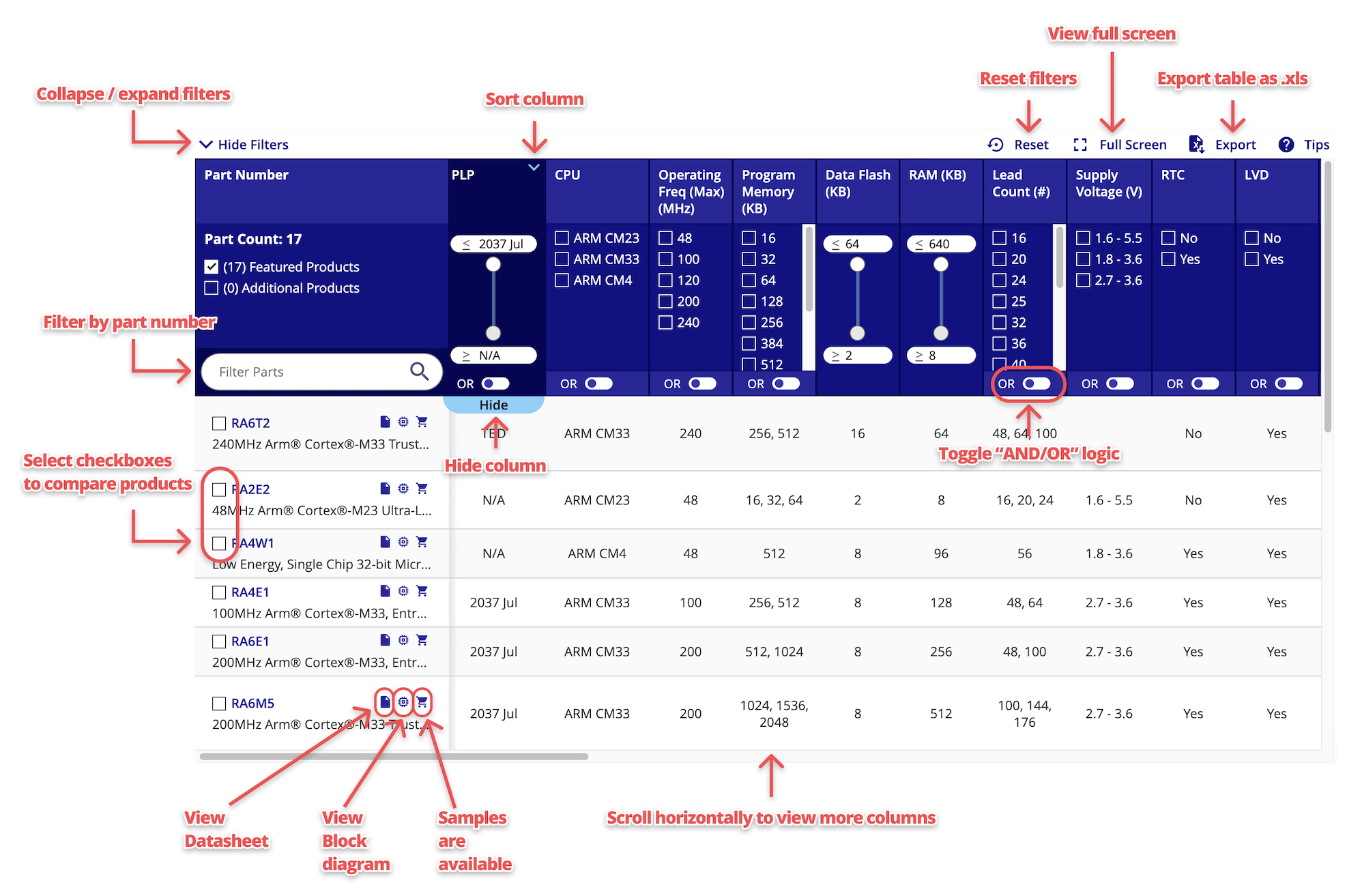

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

Videos & Training

The 8V19N880 and 8V19N882 JESD204B/C clock jitter attenuators deliver low phase noise and exceptional jitter performance as low as 74fs RMS and -90dB spurious attenuation for mission-critical industrial data converter applications in wireless radio, test and measurement, instrumentation, and high-performance imaging. They support frequencies up to 3932.16MHz (up to 6GHz with an external VCO) and feature 16 and 18 integrated differential outputs to deliver a first-in-class balance of high performance, low voltage and low power consumption with 1.8V support.

News & Blog Posts

|

Your Guide to Executing pcm4l Software Flawlessly | Blog Post | Jan 30, 2021 |