概要

説明

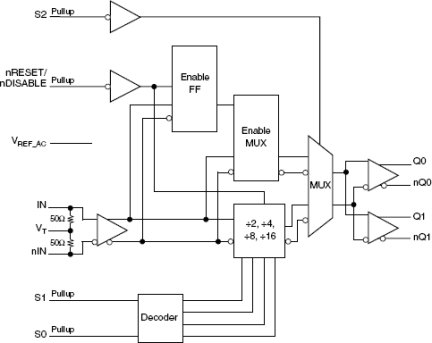

The 8S89876I is a high speed Differential-to-LVDS Buffer/Divider w/Internal Termination. The 8S89876I has a selectable ÷1, ÷2, ÷4, ÷8, ÷16 output divider. The clock input has internal termination resistors, allowing it to interface with several differential signal types while minimizing the number of required external components. The device is packaged in a small, 3mm x 3mm VFQFN package, making it ideal for use on space-constrained boards.

特長

- Two LVDS outputs

- Frequency divide select options: ÷1, ÷2, ÷4, ÷8, ÷16

- IN, nIN input can accept the following differential input levels: LVPECL, LVDS, CML

- Input Frequency: 2.5GHz (maximum)

- Additive phase jitter, RMS: 0.07ps (typical)

- Output skew: 25ps (maximum)

- Part-to-part skew: 280ps (maximum)

- Propagation Delay: 1.1ns (maximum)

- Full 3.3V supply mode

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

- Pin compatible with the obsolete device 889876AK

製品比較

アプリケーション

設計・開発

製品選択

適用されたフィルター