概要

説明

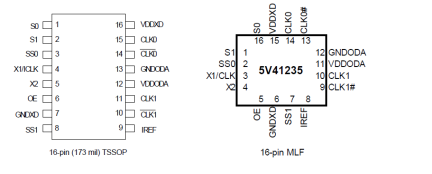

The 5V41235 is a PCIe Gen2/3 compliant spread spectrum capable clock generator. The device has 2 differential HCSL outputs and can be used in communication or embedded systems to substantially reduce electro-magnetic interference (EMI). The spread amount and output frequency are selectable via select pins. The 5V41235 can also supply 25 MHz, 125 MHz and 200 MHz outputs for applications such as Ethernet.

特長

-

2 - 0.7V current mode differential HCSL output pairs

-

16-pin TSSOP and MLF packages; small board footprint

-

Spread-spectrum capable; reduces EMI

-

Outputs can be terminated to LVDS; can drive a wider variety of devices

-

25 MHz, 125 MHz and 200 MHz output frequencies; TSSOP only

-

100MHz and 200MHz output frequencies; MLF package

-

OE control pin; greater system power management

-

Spread% and frequency pin selection; no software required to configure device

-

Industrial temperature range available; supports demanding embedded applications

-

Cycle-to-cycle jitter < 100 ps

-

Output-to-output skew < 50 ps

-

PCIe Gen2 phase jitter < 3.0ps RMS

-

PCIe Gen3 phase jitter <1.0ps RMS

製品比較

アプリケーション

設計・開発

製品選択

適用されたフィルター

ビデオ&トレーニング

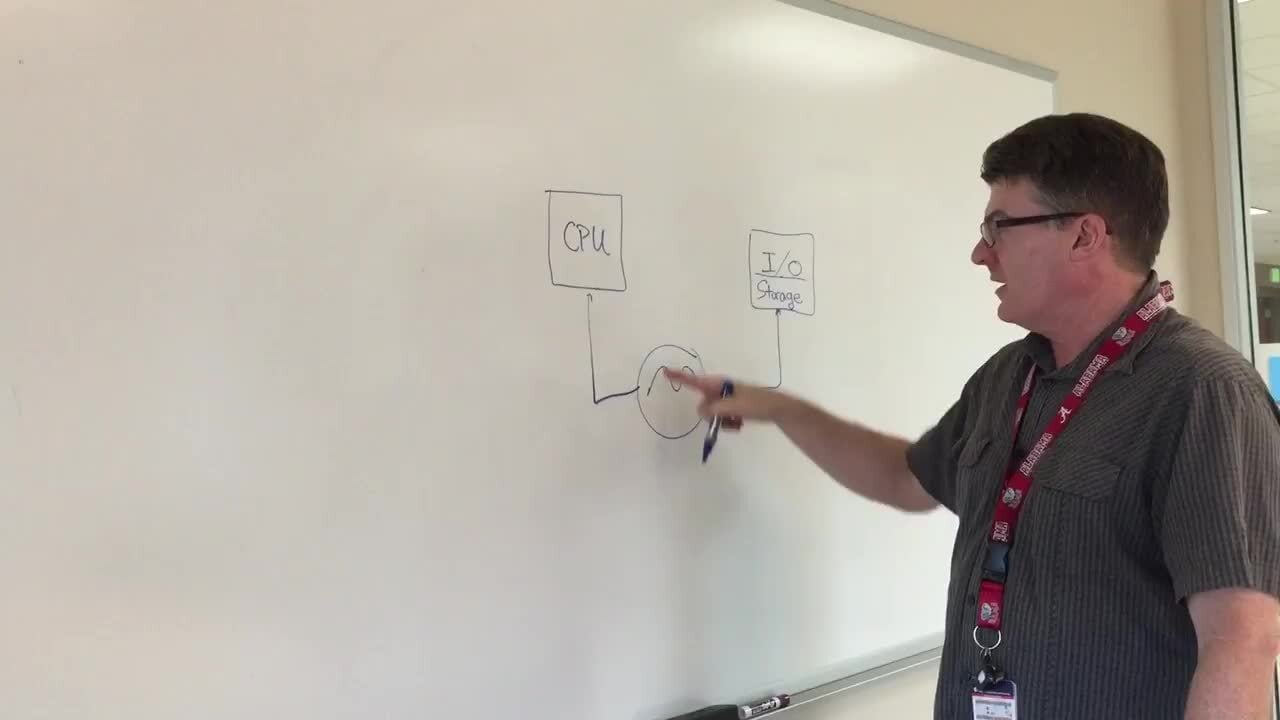

PCIe Clocking Architectures (Common and Separate)

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below

Video List