概要

説明

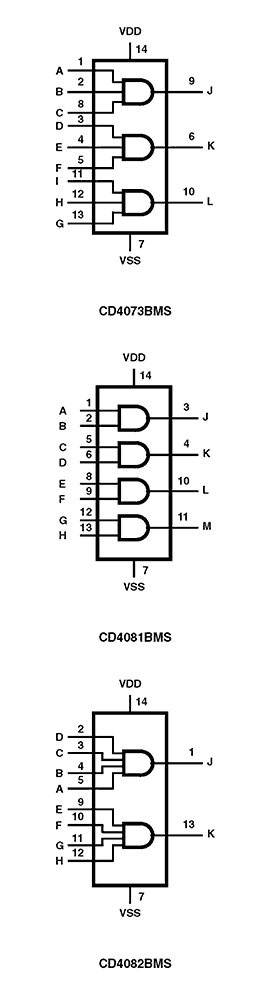

CD4073BMS, CD4081BMS and CD4082BMS AND gates provide the system designer with direct implementation of the AND function and supplement the existing family of CMOS gates.

特長

- High-voltage types (20V Rating)

- CD4073BMS triple 3-input AND gate

- CD4081BMS quad 2-input AND gate

- CD4082BMS dual 4-input AND gate

- Medium-speed operation: tPLH, tPHL = 60ns (typ) at VDD = 10V

- 100% tested for quiescent current at 20V

- Maximum input current of 1µA at 18V over full package temperature range; 100nA at 18V and +25 °C

- Noise margin (over full package temperature range): 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Standardized symmetrical output characteristics

- 5V, 10V and 15V parametric ratings

- Meets all requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

製品比較

アプリケーション

ドキュメント

ピックアップ

ログイン後、ご登録が可能となります。

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 386 KB | |

| カタログ | PDF 467 KB | |

| EOL通知 | PDF 603 KB | |

| 価格変更のお知らせ | PDF 360 KB | |

| その他資料 | ||

| 製品アドバイザリ | PDF 499 KB | |

| 製品変更通知 | PDF 230 KB | |

7件

|

||

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター