概要

説明

Support is limited to customers who have already adopted these products.

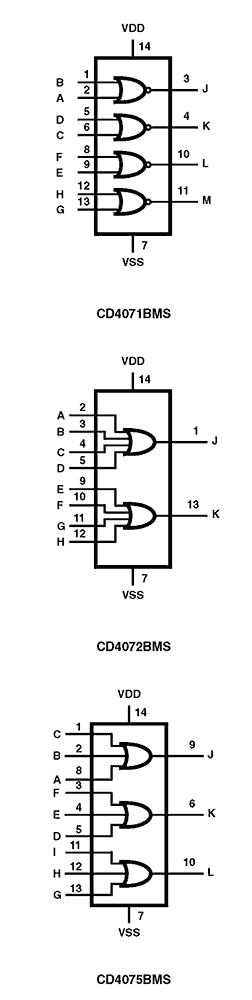

CD4071BMS, CD4072BMS and CD4075BMS OR gates provide the system designer with direct implementation of the positive-logic OR function and supplement the existing family of CMOS gates. The CD4071BMS, CD4072BMS and CD4075BMS are supplied in these 14 lead outline packages: Braze Seal DIP *H4H †H4Q Frit Seal DIP H1B Ceramic Flatpack H3W *CD4071, CD4072 †CD4075 Only

特長

- High-Voltage Types (20V Rating)

- CD4071BMS Quad 2-Input OR Gate

- CD4072BMS Dual 4-Input OR Gate

- CD4075BMS Triple 3-Input OR Gate

- Medium Speed Operation: tPHL, tPLH = 60ns (typ) at 10V

- 100% Tested for Quiescent Current at 20V

- Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and +25°C

- Standardized Symmetrical Output Characteristics

- Noise Margin (Over Full Package Temperature Range): 1V at VDD = 5V 2V at VDD = 10V 2.5V at VDD = 15V

- 5V, 10V and 15V Parametric Ratings

- Meets All Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

製品比較

アプリケーション

ドキュメント

ピックアップ

ログイン後、ご登録が可能となります。

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 391 KB | |

| カタログ | PDF 467 KB | |

| EOL通知 | PDF 200 KB | |

| 製品アドバイザリ | PDF 499 KB | |

| 製品変更通知 | PDF 230 KB | |

5件

|

||

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター