概要

説明

Support is limited to customers who have already adopted these products.

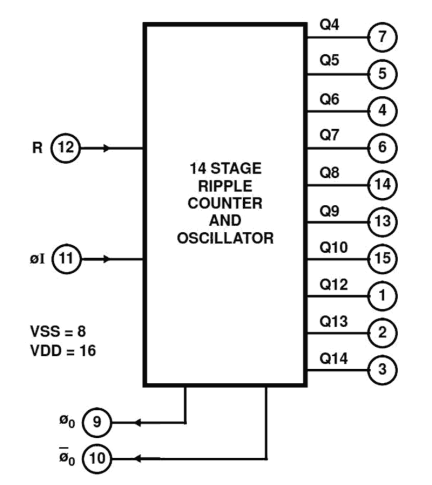

CD4060BMS consists of an oscillator section and 14 ripple carry binary counter stages. The oscillator configuration allows design of either RC or crystal oscillator circuits. A RESET input is provided which resets the counter to the all O's state and disables the oscillator. A high level on the RESET line accomplishes the reset function. All counter stages are master slave flip-flops. The state of the counter is advanced one step in binary order on the negative transition of θI (and θ0). All inputs and outputs are fully buffered. Schmitt trigger action on the input pulse line permits unlimited input pulse rise and fall times. The CD4060BMS is supplied in these 16 lead outline packages: Braze Seal DIP H4W Frit Seal DIP H1F Ceramic Flatpack H6W

特長

- High Voltage Type (20V Rating)

- Common Reset

- 12MHz Clock Rate at 15V

- Fully Static Operation

- Buffered Inputs and Outputs

- Schmitt Trigger Input Pulse Line

- Standardized, Symmetrical Output Characteristics

- 100% Tested for Quiescent Current at 20V

- 5V, 10V and 15V Parametric Ratings

- Meets All Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター