概要

説明

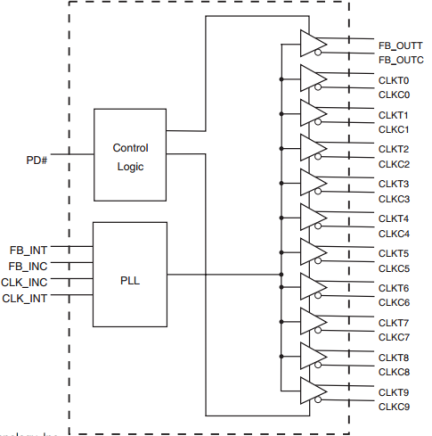

2.5V Wide Range Frequency DDR1 Clock Driver (45MHz - 233MHz)

特長

- Low skew, low jitter PLL clock driver

- 1 to 10 differential clock distribution (SSTL_2)

- Feedback pins for input to output synchronization

- PD# for power management

- Spread Spectrum-tolerant inputs

- Auto PD when input signal removed

- Choice of static phase offset available, for easy board tuning

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター