概要

説明

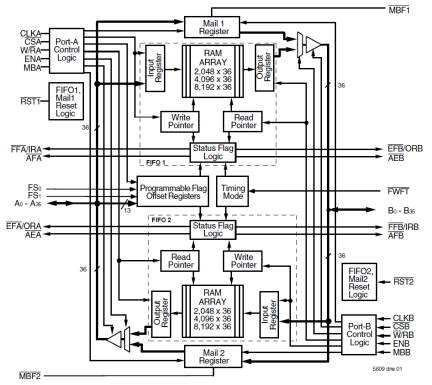

The 723672 is a Bidirectional SyncFIFO (clocked) memory. Two independent 8,192 x 36 dual-port SRAM FIFOs on board each chip buffer data in opposite directions. Communication between each port may bypass the FIFOs via two 36-bit mailbox registers. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses with synchronous control.

特長

- Supports clock frequencies up to 83MHz

- Fast access times of 8ns

- Free-running CLKA and CLKB may be asynchronous or coincident (simultaneous reading and writing of data on a single clock edge is permitted)

- Two independent clocked FIFOs buffering data in opposite directions

- Mailbox bypass register for each FIFO

- Programmable Almost-Full and Almost-Empty flags

- Microprocessor Interface Control Logic

- Available in 132-pin PQFP and 120-pin TQFP packages

- Pin compatible to the lower density 7236x2 devices

- Industrial temperature range (–40C to +85C) is available

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター