Overview

Description

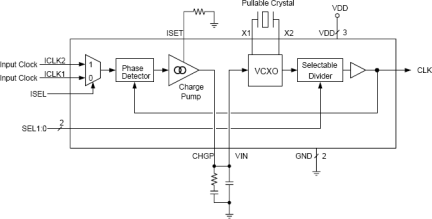

The 2059-02 is a VCXO (Voltage Controlled Crystal Oscillator) based clock multiplier and jitter attenuator designed for system clock distribution applications. This monolithic IC, combined with an external inexpensive quartz crystal, can be used to replace a more costly hybrid VCXO retiming module. A dual input mux is also provided. By controlling the VCXO frequency within a phase-locked loop (PLL), the output clock is phase and frequency locked to the input clock. Through selection of external loop filter components, the PLL loop bandwidth and damping factor can be tailored to meet system clock requirements. A loop bandwidth down to the Hz range is possible.

Features

- Excellent jitter attenuation for telecom and video clocks

- 2:1 Input MUX for input reference clocks

- No switching glitches on output

- VCXO-based clock generation offers very low jitter and phase noise generation

- Output clock is phase and frequency locked to the selected input reference clock

- Fixed input to output phase relationship

- +115 ppm minimum crystal frequency pullability range, using recommended crystal

- Industrial temperature range

- Low power CMOS technology

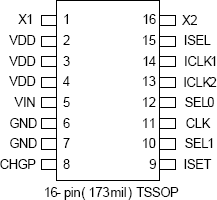

- 16-pin TSSOP package

- Single 3.3 V power supply

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on the CAD Model links in the Product Options table. If a symbol or model isn't available, it can be requested directly from SamacSys.

Product Options

Applied Filters: