Package Information

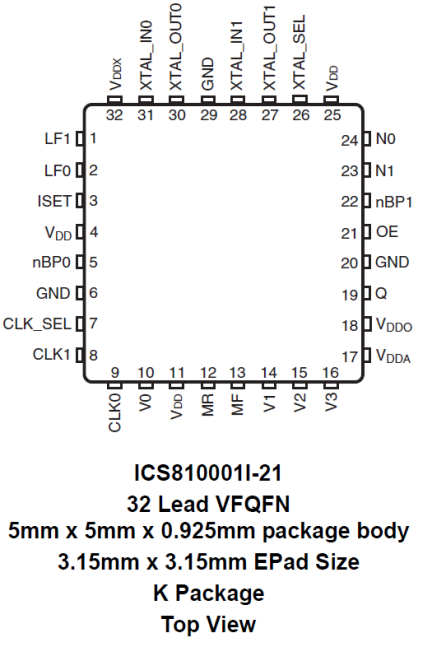

| Lead Count (#) | 32 |

| Pkg. Type | VFQFPN |

| Pkg. Code | NLG32 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 5.0 x 5.0 x 0.9 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN | NLR |

| HTSUS | 8542390001 |

Product Attributes

| Pkg. Type | VFQFPN |

| Lead Count (#) | 32 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range | -40 to +85°C |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 0.015609 - 74.3243 |

| Input Type | LVCMOS |

| Inputs (#) | 2 |

| Length (mm) | 5 |

| MOQ | 2500 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 14 - 175 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 1 |

| Package Area (mm²) | 25.0 |

| Phase Jitter Typ RMS (ps) | 1.089 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 5.0 x 5.0 x 0.9 |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 0.9 |

| Width (mm) | 5 |

Description

The 810001I-21 is a PLL-based synchronous clock generator that is optimized for digital video clock jitter attenuation and frequency translation. The device contains two internal frequency multiplication stages that are cascaded in series. The first stage is a VCXO PLL that is optimized to provide reference clock jitter attenuation and to support the complex PLL multiplication ratios needed for video rate conversion. The second stage is a FemtoClock™ frequency multiplier that provides the low jitter, high-frequency video output clock.

Preset multiplication ratios are selected from internal lookup tables using device input selection pins. The multiplication ratios are optimized to support most common video rates used in professional video system applications. The VCXO requires the use of an external, inexpensive pullable crystal. Two crystal connections are provided (pin selectable) so that both 60Hz and 59.94Hz base frame rates can be supported. The VCXO requires external passive loop filter components which are used to set the PLL loop bandwidth and damping characteristics.