概要

説明

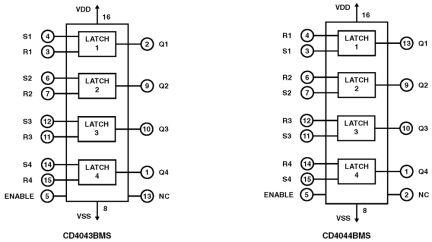

The CD4043BMS devices are quad cross-coupled 3-state CMOS NOR latches and the CD4044BMS devices are quad cross-coupled 3-state CMOS NAND latches. Each latch has a separate Q output and individual Set and Reset inputs. The Q outputs are controlled by a common Enable input. A logic 1 or high on the Enable input connects the latch states to the Q outputs. A logic 0 or low on the Enable input disconnects the latch states from the Q outputs; this results in an open circuit feature allowing for common busing of the outputs. The CD4043BMS and CD4044BMS are supplied in these 16- lead outline packages: Braze Seal DIP H4T, Frit Seal DIP H1C (CD4043BMS) and HIE (CD4044BMS), and Ceramic Flatpack H3X (CD4043BMS) and H6W (CD4044BMS).

特長

- High-voltage types (20V rating)

- Quad NOR R/S latch- CD4043BMS

- Quad NAND R/S latch - CD4044BMS

- 3-state outputs with common output Enable

- Separate Set and Reset inputs for each latch

- NOR and NAND configuration

- 5V, 10V and 15V parametric ratings

- Standardized symmetrical output characteristics

- 100% tested for quiescent current at 20V

- Maximum input current of 1µa at 18V over full package temperature range; 100nA at 18V and 25 °C

- Noise margin (over full package temperature range): 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets all requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

製品比較

アプリケーション

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 387 KB | |

| カタログ | PDF 467 KB | |

| 価格変更のお知らせ | PDF 360 KB | |

| その他資料 | ||

| 製品アドバイザリ | PDF 499 KB | |

| 製品変更通知 | PDF 230 KB | |

6件

|

||

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター