Overview

Description

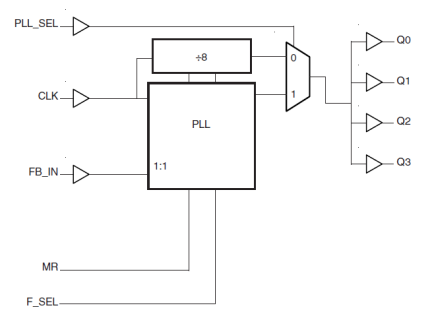

The 86004 is a high performance 1:4 LVCMOS/LVTTL Clock Buffer. The 86004 has a fully integrated PLL and can be configured as zero delay buffer and has an input and output frequency range of 15.625MHz to 62.5MHz. The VCO operates at a frequency range of 250MHz to 500MHz. The external feedback allows the device to achieve "zero delay" between the input clock and the output clocks. The PLL_SEL pin can be used to bypass the PLL for system test and debug purposes. In bypass mode, the reference clock is routed around the PLL and into the internal output divider.

Features

- Four LVCMOS/LVTTL outputs, 7 Ohms typical output impedance

- Single LVCMOS/LVTTL clock input

- CLK accepts the following input levels: LVCMOS or LVTTL

- Output frequency range: 15.625MHz to 62.5MHz

- Input frequency range: 15.625MHz to 62.5MHz

- VCO range: 250MHz to 500MHz

- External feedback for "zero delay" clock regeneration with configurable frequencies

- Fully integrated PLL

- Cycle-to-cycle jitter: 65ps (maximum)

- Output skew: 65ps (maximum)

- Full 3.3V or 2.5V, or 3.3V core/2.5V output operating supply

- 0°C to 70° ambient operating temperature

- Available in lead-free RoHS compliant package

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.