概要

説明

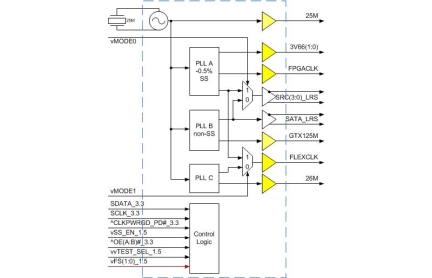

The IDT5U49319 is a very low power clock for Freescale P10xx and P20xx MCU’s. It uses a 1.5V core and Low-Power HCSL (LP-HCSL) differential outputs for minimal power consumption. The SATA and SRC outputs are PCIe Gen1/2 compatible.

特長

- Various outputs are configurable to run in power down; supports Wake_On_LAN

- FPGA clock frequency is selectable via SMBus; allows low-power system standby

- Strapping pin sources SRC outputs from either spreading or non-spreading PLL; maximum system flexibility

- FLEX clock is pin selectable to be FPGA clock or USB PHY clock; maximum system flexibility

- TEST pin tri-states all outputs; speeds up board test

- External 25MHz crystal; supports tight ppm

- OE# pins; support SRC power management

- Low power differential clock outputs; reduced power and board space

- Differential outputs internally terminated to 100ohm differential impedance; reduced board space

- Space-saving 7x7mm 48-pin VFQFPN with 0.5mm pad pitch; reduced board space without the need for fine pitch assembly techniques

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

SamacSysの回路図シンボル、PCBフットプリント、および3D CADモデルは、製品オプションテーブルのCADモデルリンクをクリックすることで参照できます。シンボルまたはモデルが対応していない場合は、SamacSysに直接リクエスト可能です。

製品選択

適用されたフィルター