Overview

Description

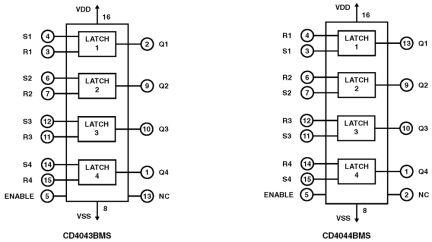

The CD4043BMS devices are quad cross-coupled 3-state CMOS NOR latches and the CD4044BMS devices are quad cross-coupled 3-state CMOS NAND latches. Each latch has a separate Q output and individual Set and Reset inputs. The Q outputs are controlled by a common Enable input. A logic 1 or high on the Enable input connects the latch states to the Q outputs. A logic 0 or low on the Enable input disconnects the latch states from the Q outputs; this results in an open circuit feature allowing for common busing of the outputs. The CD4043BMS and CD4044BMS are supplied in these 16- lead outline packages: Braze Seal DIP H4T, Frit Seal DIP H1C (CD4043BMS) and HIE (CD4044BMS), and Ceramic Flatpack H3X (CD4043BMS) and H6W (CD4044BMS).

Features

- High-voltage types (20V rating)

- Quad NOR R/S latch- CD4043BMS

- Quad NAND R/S latch - CD4044BMS

- 3-state outputs with common output Enable

- Separate Set and Reset inputs for each latch

- NOR and NAND configuration

- 5V, 10V and 15V parametric ratings

- Standardized symmetrical output characteristics

- 100% tested for quiescent current at 20V

- Maximum input current of 1µa at 18V over full package temperature range; 100nA at 18V and 25 °C

- Noise margin (over full package temperature range): 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets all requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

Comparison

Applications

Applications

- Holding register in multi-register system

- Four bits of independent storage with output Enable

- Strobed register

- General digital logic

- CD4043BMS for positive logic systems

- CD4044BMS for negative logic systems

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.