Overview

Description

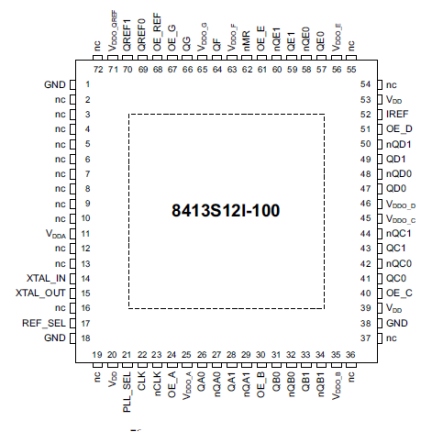

The 8413S12I-100 is a PLL-based clock generator specifically designed for Cavium Networks Octeon II processors. This high-performance device is optimized to generate the processor core reference clock, the PCI Express reference clocks, and the clocks for both the Gigabit Ethernet MAC and PHY. The clock generator offers ultra-low jitter, low-skew clock outputs, and edge rates that easily meet the input requirements for the CN63XX and CN68XX series of processors. The output frequencies are generated from a 25MHz external input source or an external 25MHz parallel resonant crystal. The industrial temperature range of the 8413S12I-100 supports telecommunication, networking, and storage requirements.

Features

- Ten 100MHz clocks for PCI Express, HCSL interface levels

- One single-ended QG LVCMOS/LVTTL clock output at 125MHz

- One single-ended QF LVCMOS/LVTTL clock output at 50MHz, 15Ω output impedance

- Two single-ended QREFx LVCMOS/LVTTL outputs at 25MHz, 15Ω output impedance

- Selectable external crystal or differential (single-ended) input source

- Crystal oscillator interface designed for 25MHz, parallel resonant crystal

- Differential CLK, nCLK input pair that can accept: LVPECL, LVDS, LVHSTL, and HCSL input levels

- Internal resistor bias on nCLK pin allows the user to drive CLK input with external single-ended (LVCMOS/ LVTTL) input levels

- Supply modes, (125MHz QG output and 25MHz QREFx outputs):

Core/Output

3.3V/3.3V

3.3V/2.5V - Supply modes, (HCSL outputs, and 50MHz QF output):

Core/Output

3.3V/3.3V - -40 °C to 85 °C ambient operating temperature

- Available in a lead-free (RoHS 6) package

Comparison

Applications

Applications

- Systems using Cavium Processors

- CPE Gateway Design

- Home Media Servers

- 802.11n AP or Gateway

- Soho Secure Gateway

- Soho SME Gateway

- Wireless Soho and SME VPN Solutions

- Wired and Wireless Network Security

- Web Servers and Exchange Servers

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.