Overview

Description

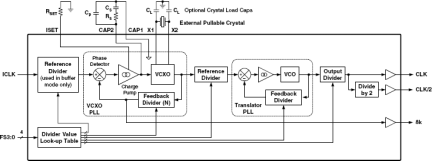

The MK2049-45A is a dual Phase-Locked Loop (PLL) device that can provide frequency synthesis and jitter attenuation. The first PLL is VCXO-based and uses a pullable crystal to track signal wander and attenuate input jitter. The second PLL is a translator for frequency multiplication. Basic configuration is determined by a Mode/Frequency Selection Table. Loop bandwidth and damping factor are programmable via external loop filter component selection. Buffer Mode accepts a 10MHz to 50MHz input and will provide a jitter attenuated output at 0.5 x ICLK, 1 x ICLK, or 2 x ICLK. In this mode, the MK2049-45A is ideal for filtering jitter from high-frequency clocks. In External Mode, ICLK accepts an 8kHz clock and will produce output frequencies from a table of common communications clock rates, CLK and CLK/2. This allows for the generation of clocks frequency-locked to an 8kHz backplane clock, simplifying clock synchronization in communications systems. The MK2049-45A can be dynamically switched between T1, E1, T3, and E3 outputs with the same 24.576MHz crystal. Renesas can customize these devices for many other different frequencies.

Features

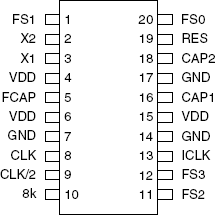

- Packaged in a 20-pin SOIC

- 3.3V + 5% operation

- Meets the TR62411, ETS300 011, and GR-1244 specifications for MTIE, Pull-in/Hold-in Range, Phase Transients, and Jitter Generation for Stratum 3, 4, and 4E

- Accepts multiple inputs: 8kHz backplane clock, or 10MHz to 50MHz

- Locks to 8kHz + 100ppm (External mode)

- Buffer Mode allows jitter attenuation of 10MHz to 50 MHz input and x1 / x0.5 or x1 / x2 outputs

- Exact internal ratios enable zero ppm error

- Output rates include T1, E1, T3, E3, and OC3 submultiples

- Pb (lead) free package

- See also the MK2049-34 and MK2049-36

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.