Overview

Description

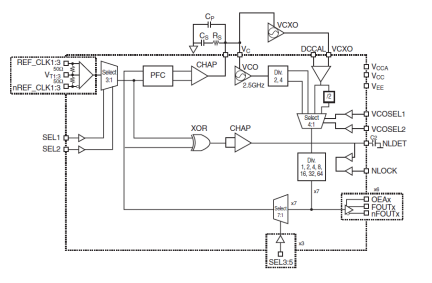

The 843S06 is a low voltage, low skew 3.3V LVPECL Clock Synthesizer. The device targets clock distribution in SDH/SONET telecommunication systems but is well suited for a wide range of applications requiring high performance high-speed clock synthesis. The device implements a fully integrated multiplying PLL including:

Features

- 6 differential 3.3V LVPECL outputs1,244.16 / 622.08MHz

- 1,244.16 / 622.08MHz 622.08 / 311.04MHz

- 311.04 / 155.52MHz 155.52 / 77.76MHz

- 77.76/38.88MHz

- Three selectable differential reference clock inputsClock frequency range: 19MHz to 622MHz

- REF_CLKx, nREF_CLKx pairs can accept the followingdifferential input level: LVPECL

- Intrinsic jitter: 0.017mUIRMS @ 622MHz

- Output skew: 200ps (maximum)

- Optional external VCXO possible

- Simple external loop filter

- Lock detect output signal

- Full 3.3V operating supply

- Low power operation 0.6W (typical)

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) packages

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.