Overview

Description

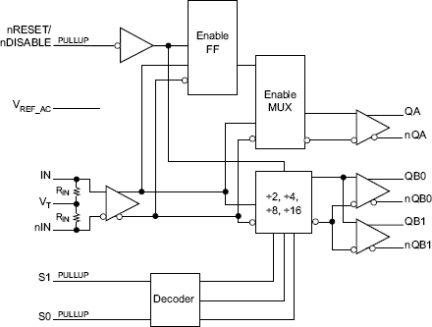

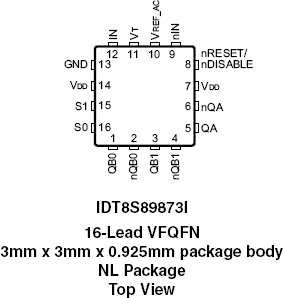

The 8S89873 is a high-speed Differential-to-LVDS Buffer/Divider with Internal Termination. The 8S89873 has a selectable ÷2, ÷4, ÷8, ÷16 output dividers. The clock input has internal termination resistors, allowing it to interface with several differential signal types while minimizing the number of required external components. The device is packaged in a small, 3mm x 3mm VFQFN package, making it ideal for use on space-constrained boards.

Features

- Three LVDS outputs

- Frequency divide select options: ÷2, ÷4, ÷8, ÷16

- IN, nIN input can accept the following differential input levels: LVPECL, LVDS, CML

- Output frequency: 2GHz (maximum) in pass-through mode

- Additive phase jitter: 0.185ps (typical) RMS

- Output skew: 9ps (typical), QBx, nQBx outputs

- Propagation Delay: 540ps (typical)

- Full 3.3V supply mode

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.