Overview

Description

[Upgrade to Revision] RH850 Model-Based Development Environment, Embedded Target for RH850 Multicore + Multirate V5.02.00, Embedded Target for RH850 Multicore V5.02.00, Embedded Target for RH850 V5.02.00 (PDF | English, 日本語)

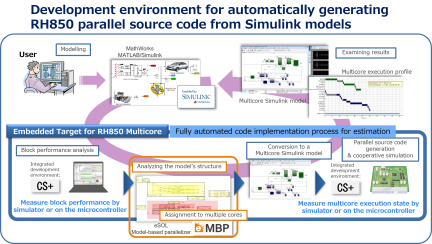

The Embedded Target for RH850 Multicore is a RH850 model-based multicore environment that simplifies complex driving control for the autonomous-driving era. In addition to the multicore support of the PILS (Note) tool for automatic configuration of environments, Embedded Target for Renesas CS+, it can also be interlinked with a model-based parallelization tool from eSOL Co., Ltd.

In addition, Embedded Target for RH850 Multicore + Multirate can directly and automatically generate parallelized code for multicore devices that are to run code from control models for engines, vehicle bodies and so on, which will, in general, require multiple control periods (requiring multi-rate control).

The Embedded Target for RH850 Multicore generates parallel code for multicore RH850 devices through the implementation phase of a Simulink® model from The MathWorks®, Inc. It contributes to innovative automotive control systems for “eco-cars” (fuel economy and CO2 regulation) and to enhanced safety through the evaluation of functionality and performance in the flow of development.

Features

- This enables evaluation of the operation of systems with multiple control periods, such as systems for controlling engines and bodies, and ECUs (Electronic Control Units), in which multiple systems for controlling various items in the vehicle as a whole are integrated.

- The generated schedulers are conformant with the type α control model that the MathWorks Automotive Advisory Board (MAAB) recommends in the Control Algorithm Modeling Guidelines.

- Automatically generated code is of the multi-rate single-task type and runs on multicore devices without an OS.

- The allowable margins for processing, for which the worst execution timespans during simulation are going to be the control periods, can be checked

- Graphical display of the states of execution for each core in sub-system units of Simulink models

- Acquisition of execution times in sub-system units at the time of simulation through the debugger of CS+

- Graphical display of the states of execution for each core in sub-system units

- This makes it possible to compare and examine which software structures make effective use of the capacity of the multiple cores directly on MATLAB® and Simulink models

- Automatically finds the best allocations of cores for complex innovative control systems then parallelizes them

- Automatically finds the best core allocations for control systems in cooperation with the MBP tool from eSOL Co., Ltd.

- Returning to earlier stages in design due to incorrect estimation of parallel performance before implementing software can be avoided, and the development times for multicore control software can be shortened

- Automatically generates parallel source code and provides visualization of the performance of multiple cores during modelling

- Cycle-accurate simulators as optional features of CS+, which allow the measurement of times that closely reflect those of actual systems. (For some of the RH850 MCUs) [Cycle-Accurate Simulator for RH850]

- Learn More

Release Information

- The Embedded Target for RH850, which supports the block unit performance analysis of the single core is also available.

- To purchase the tool, contact your local Renesas Electronics marketing office or distributor for release date.

Latest Ver.: V5.02.00

Released: Dec 16, 2021

Release information (See Tool News)

Operating Environment

Type of License

Annual license, i.e. a license with a one-year expiry period. Contact your nearest Renesas distributor with regard to purchasing products.

For customer who consider commercial version of this tool

We recommend that you check operating environments of this tool carefully and try the free evaluation version (limited 3 months usage) on your development environment first to check if it works properly. In particular, when performing detailed time measurements on an actual device, a target device equipped with trace RAM is required.

Again, please check operating environments of the Embedded Target for RH850 carefully.

Evaluation Version Information

After obtaining this tool from the download list, please request the license key from your distributor or our sales representative, or follow the steps below.

- Access technical support on the Renesas Web site.

- Click on [LOG IN] and log in to the site with your ID which has been registered with My Renesas.

- Click on [SUBMIT A TICKET] in the upper right of the screen.

- Issue a new ticket by referring to the table and examples of entry which are shown to the right side.

Title: Request a License Key for Evaluation version of the Embedded Target for RH850 Multicore + Multirate

MCU Product Family: Target device using this tool (RH850/F1KM, etc.)

Description: Describe the purpose for use, field of application for Embedded Target and your previous experience in using model-based development environments including MATLAB® and experience (or plans) for using our target device.

Note: MATLAB®, Simulink® are registered trademarks of The MathWorks, Inc.

Target Devices

Embedded Target for RH850 Multicore + Multirate and Embedded Target for RH850 Multicore support the MCUs listed below.

Contact our distributors regarding our plans in regard to support for the other MCUs, i.e. those for which we do not currently provide a cycle-accurate simulator.

| Series | Applicable MCU | Cycle-accurate simulator |

|---|---|---|

| RH850/C1x | RH850/C1H, RH850/C1M-A1, RH850/C1M-A2 | Yes |

| RH850/E1x | RH850/E1M-S2 (Note1) | Please contact us. |

| RH850/F1x | RH850/F1L、 RH850/F1H | Please contact us. |

| RH850/F1Kx | RH850/F1K、RH850/F1KM、RH850/F1KH | Yes |

| RH850/P1x | RH850/P1H-C、 RH850/P1M、 RH850/P1M-C、 RH850/P1M-E | Yes |

| RH850/E2x | RH850/E2M, RH850/E2UH, RH850/E2H | Yes |

Note

- Use only main CPU.

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Flyer | PDF 306 KB 日本語 | |

| Tool News - Release | PDF 206 KB 日本語 | |

| Flyer | PDF 803 KB 日本語 | |

3 items

|

||

Videos & Training

News & Blog Posts

| Blog Post | Jan 23, 2021 |

Additional Details

Functions

- Generation of code for verifying algorithms from Simulink models

- Automatic generation of Processor in the Loop Simulation (PILS) environments

Flow of Operations

- Measuring execution times: The execution times of a Simulink model are measured in sub system units by using the software trace function of the debugger of CS+ on PILS of a single core. (This function is also supported even Embedded Target for RH850.)

- Finding the optimal core allocation: A search for the best core allocation based on the execution times acquired in step 1 is conducted through interlinked operation with the optional “eSOL MBP Renesas RH850 MBD Package” (provisional name) of the Model-Based Parallelizer (provisionally referred to as eSOL MBP in this document) from eSOL, and parallelization proceeds.

- Code generation: Synchronous processing is automatically allocated among the cores in accord with the core allocation plan from the model-based parallelization tool or an allocation plan specified by the user, and parallel source code for the RH850 is generated by the Embedded Coder from The MathWorks, Inc.

- Re-measuring execution time: The execution times with the cores having been allocated in sub-system units are acquired by the debugger function of CS+, and the states of execution for each core are displayed in a graph.

Comparison of the Functions of Embedded Target Products

| Function | |||||||

|---|---|---|---|---|---|---|---|

| PIL Simulation on Single-Core Products (Supports multi-rate control) | PIL Simulation on Multicore Products | Load Module Generation by GHS Compiler | Performance Analysis in Blocks | Interlinking with eMBP | |||

| One Core Used | Multiple Cores Used | ||||||

| License Type | Embedded Target for RH850 Multicore + Multirate - RH850 multicore multirate version | lens | lens (Note1) | lens (Note1) | lens | lens | lens (Note2) |

| Embedded Target for RH850 Multicore - RH850 multicore version | lens | lens | lens | lens | lens | lens | |

| Embedded Target for RH850 - RH850 single-core version | lens | — | — | lens | lens | — | |

lens Supported | — Not supported

Notes

1. Supports multi-rate control

2. Support for multi-rate control is in planning.

Related Information

- News Release from Renesas Electronics Corporation (Renesas Electronics Updates Model-Based Development Environment to Significantly Ease Software Development Burdens for Multi-Core Automotive Control Microcontrollers)

- Demonstration of [Flyer] RH850 Model-Based Development Environment for Multi-Rate Control (PDF | English, 日本語) at the MathWorks Automotive Conference 2018

- News Release from Renesas Electronics Corporation (2016) (Renesas Electronics Develops RH850 Multicore Model-Based Environment to Simplify Implementation of Cruise Control in Autonomous Vehicles)

- News release from eSOL Co., Ltd.

- Blog: Customer Value of Automotive Business (Series 20): Starting the Multicore Model Based Development with Embedded Target for RH850 Multicore