概要

説明

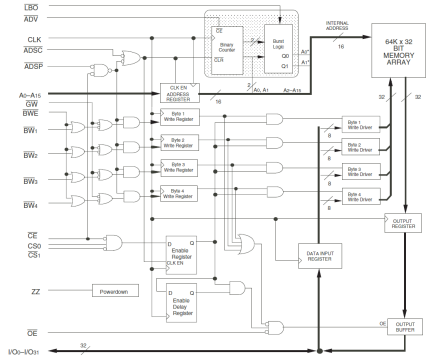

The 71V632 3.3V CMOS SRAM is organized as 64K x 32. The pipelined burst architecture provides cost-effective 3-1-1-1 secondary cache performance for processors up to 117MHz. The 71V632 SRAM contains write, data, address, and control registers. The burst mode feature offers the highest level of performance to the system designer, as it can provide four cycles of data for a single address presented to the SRAM.

特長

- High system speed 4.5ns clock access time (117 MHz)

- Single-cycle deselect functionality (Compatible with

- Micron Part # MT58LC64K32D7LG-XX)

- LBO input selects interleaved or linear burst mode

- Self-timed write cycle with global write control (GW), byte

- write enable (BWE), and byte writes (BWx)

- Power down controlled by ZZ input

- Operates with a single 3.3V power supply (+10/-5%)

- Available in 100-pin TQFP package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。