概要

説明

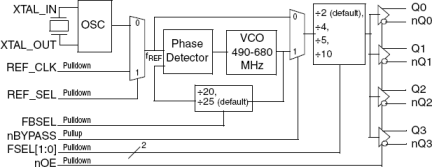

The 845254I is a 3.3V/2.5V CML clock generator designed for Ethernet applications. The device synthesizes either a 50MHz, 62.5MHz, 100MHz, 125MHz, 156.25MHz, 250MHz or 312.5MHz clock signal with excellent phase jitter performance. The clock signal is distributed to four low-skew differential CML outputs. The device is suitable for driving the reference clocks of Ethernet PHYs. The device supports 3.3V and 2.5V voltage supply and is packaged in a small, lead-free (RoHS 6) 32-lead VFQFN package. The extended temperature range supports telecommunication, wireless infrastructure and networking end equipment requirements.

特長

- Clock generation of: 50MHz, 62.5MHz, 100MHz, 125MHz, 156.25MHz, 250MHz and 312.5MHz

- Four differential CML clock output pairs

- 25MHz reference clock (selectable internal crystal oscillator and external LVCMOS clock)

- RMS phase jitter @ 125MHz, using a 25MHz crystal (1.875MHz – 20MHz): 0.405ps (typical)

Offset Noise Power

100Hz.................... -104.6 dBc/Hz

1kHz.................... -118.4 dBc/Hz

10kHz................... -124.1 dBc/Hz

100kHz................... -125.3 dBc/Hz

- LVCMOS interface levels for the control inputs

- Full 3.3V and 2.5V supply voltage

- Available in lead-free (RoHS 6) 32 VFQFN package

- -40°C to 85°C ambient operating temperature

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。