概要

説明

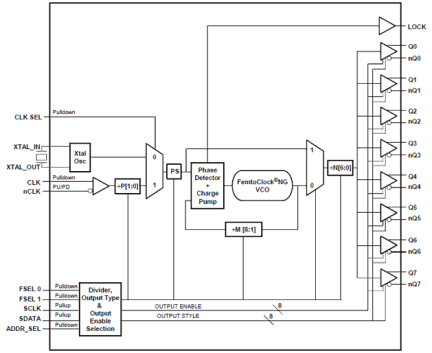

The 8T49N008I is an eight output Clock Generator with selectable LVDS or LVPECL outputs. The 8T49N008I can generate any one of four frequencies from a single crystal or reference clock. The four frequencies are selected from the Frequency Selection Table (Table 3) and are programmed via I2C interface. The four predefined frequencies are selected in the user application by two frequency selection pins. Note the desired programmed frequencies must be used with the corresponding crystal as indicated in Table 3. Excellent phase noise performance is maintained with Renesas' 4TH Generation FemtoClock™ NG PLL technology, which delivers sub-0.5ps RMS phase jitter.

特長

- 4TH Generation FemtoClock NG PLL technology

- Eight selectable LVPECL or LVDS outputs

- CLK, nCLK input pair can accept the following differential input levels: LVPECL, LVDS, HCSL

- FemtoClock NG VCO Range: 1.9GHz - 2.55GHz

- RMS phase jitter at 156.25MHz (10kHz - 1MHz): 0.223ps (typical)

- Full 2.5V or 3.3V power supply

- I2C programming interface

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

- 4-output (8T49N004I) and 6-output (8T49N006I) also available

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。