概要

説明

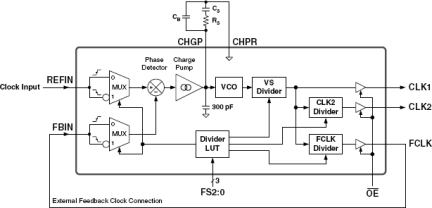

The MK1575-01 is a clock recovery Phase-Locked Loop (PLL) designed for clock synthesis and synchronization in cost sensitive applications. The device is optimized to accept a low-frequency reference clock to generate a high-frequency data or graphics pixel clock. External loop filter components allow tailoring of loop frequency response characteristics. For low jitter / phase noise requirements refer to the MK2069 products.

特長

- Long-term output jitter <2 nsec over 10 ?sec period

- External PLL clock feedback path enable "zero delay" I/O clock skew configuration

- Selectable internal feedback divider provides popular telecom and video clock frequencies (see tables below)

- Can optionally use external feedback divider to generate other output frequencies.

- Single 3.3 V supply, low-power CMOS

- Power-down mode and output tri-state (pin OE)

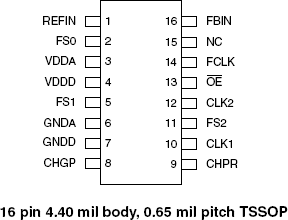

- Packaged in 16-pin TSSOP

- Pb (lead) free package

- Industrial temperature range available

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。