概要

説明

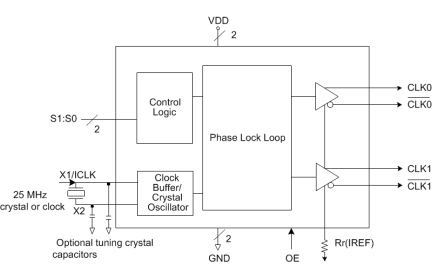

The IDT5V41285 is a PCIe Gen2 compliant clock generator. The device has 2 differential HCSL outputs. The output frequency is selectable via select pins.

特長

- 16-pin TSSOP and VFQFPN packages; small board footprint

- Outputs can be terminated to LVDS; can drive a wider variety of devices

- OE control pin; greater system power management

- Industrial temperature range available; supports demanding embedded applications

- Cycle-to-cycle jitter: 80ps

- Output-to-output skew <50 ps

- PCIe Gen2 phase jitter <3.0ps RMS

- Low phase noise: 12kHz to 20MHz <6ps

- For PCIe Gen3 applications, see the IDT5V41315

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

ビデオ&トレーニング

PCIe Clocking Architectures (Common and Separate)

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below

Video List