概要

説明

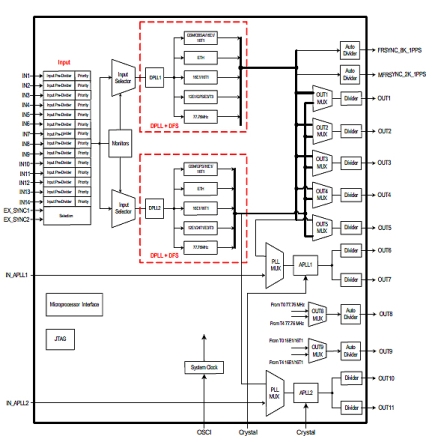

The 82V3910 is a single-chip Synchronous Equipment Timing Source (SETS) for Synchronous Ethernet (SyncE). The 82V3910 complies with ITU-T G.8262 for EEC Options 1 and 2; and G.813 for SEC Options 1 and 2; it is suitable for SyncE, SONET, and SDH equipment. Its ultra-low jitter generation makes it particularly suitable for single-board systems where the SETS directly times 10GBASE-R, 10GBASE-W, OC-192/STM-64, or 40GBASE-R PHYs.

The high-integration architecture minimizes component count and board space by including a “T0” G.8262 compliant digital PLL (DPLL); and a “T4” rate converting DPLL to provide recovered line timing to a local Building Integrated Timing Supply (BITS) or Synchronization Supply Unit (SSU). Two independent jitter attenuating analog PLLs (APLLs) are also integrated; these APLLs generate clocks with jitter below 0.3ps RMS over the 10kHz to 20MHz integration range and can be used to directly time 10GbE or 40GbE network PHYs. The DPLLs lock to a wide variety of telecom and Ethernet reference frequencies and suppress incoming timing faults to generate highly reliable output clocks for optimal network performance. The T0 DPLL can lock directly to a one pulse-per-second (1 PPS) reference enabling the host system to use a low-cost GPS receiver for synchronization.

The 82V3910 offers a solution optimized for use in Ethernet switches, routers, multi-service switching platforms, wireless backhaul equipment, and other communications infrastructure. It is available in a 196-ball 15mm x 15mm CABGA package and supports the standard industrial temperature range from -40 °C to +85 °C.

特長

- Single-chip solution for SyncE SETS

- Jitter generation < 0.3ps RMS (10kHz to 20MHz) meets the most stringent 10G PHY requirements

- Two ultra-low jitter analog PLLs support three clock modes: 622.08MHz, 625MHz, and 625MHz x 66/64

- Generates interface clocks (1GE, 10GBASE-R, 10GBASE-W, and 40GBASE-R) and SONET/SDH (OC-192/STM-64)

- Meets G.8262 for Synchronous Ethernet (SyncE) equipment

- Meets Telcordia GR-253-CORE and ITU-T G.813 for SONET/SDH equipment

- Integrates T4 DPLL and T0 DPLLs per ITU-T G.8264

- Supports input and output clocks whose frequencies range from 1PPS to 625MHz x 66/64

- Internal DCO can be controlled by an external processor to be used for IEEE 1588 clock generation

- Complemented by the 82V3911 SyncE PLL for 10GbE and 40GbE

製品比較

アプリケーション

アプリケーション

- SMC/SEC (SONET/SDH equipment)

- EEC (Synchronous Ethernet equipment)

- Core and access IP switches/routers

- Gigabit and Terabit IP switches/routers

- Cellular and WLL base station node clocks

- Broadband and multi-service access equipment

設計・開発

ソフトウェア/ツール

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。