Renesasの、IEEE 1588 および同期イーサネット向け DPLL(デジタル PLL)は、パケットスイッチ・ネットワーク上での同期用に設計されています。 IEEE1588 アプリケーションでは、IEEE 1588 クロック回復アルゴリズム用に組込みDCO(デジタル制御発振器)を低ジッター合成器として使用できます。 同期イーサネット アプリケーションでは、DPLL が EEC(同期イーサネット機器クロック)の ITU-T 勧告に準拠しています。DPLL 製品は、SONET/SDH、PDH および TDM 同期要件にも対応しています。 Renesasの DPLL 製品は、IEEE 1588 DCO モードと SyncE モードを切り替えることができます。また、選択可能ループフィルター、ホールドオーバー、ヒットレス基準スイッチング、位相スロープ制限、クロック冗長などの機能を搭載しています。

ITU-T G.8262 用の Altera および IDT 同期イーサネット ソリューションに関する ホワイトペーパー

IEEE 1588 について

IEEE 1588 は、コンピューター ネットワークにおいてクロックの同期に使用される、高精度時間プロトコル(PTP)です。 測定システムや制御システム向けに、ローカルエリアネットワーク上のデバイスをマイクロ秒以下の正確なクロックで同期させる規格です。 IEEE 1588 基準は、複数のネットワーク・セグメント、複数のクロックから構成される、クロック分配用マスタ/スレーブ・アーキテクチャを規定しています。 Renesasは業界最先端の高性能ソリューション・ポートフォリオで、IEEE 1588 のクロッキングニーズに対応しています。

同期イーサネット(SyncE)について

同期イーサネットは、コンピューターネットワーク向けの ITU-T 基準であり、イーサネット物理層におけるクロック信号の伝送方法について規定しています。 同期イーサネットの目的は、ネットワーク上のさまざまなリソースに同期信号を配信することにあります。 同期イーサネット信号は、イーサネット物理層を伝送され、外部クロックに対して追跡可能でなくてはなりません。 アプリケーションには、ルーター、マルチサービス・スイッチング・プラットフォーム、PON(受動光ネットワーク)、DSLAM(デジタル加入者線アクセス多重化装置)などがあります。 完璧なソリューションを構築するためのあらゆるタイミング部品を提供する唯一の企業として、Renesasは通信機器サプライヤーのニーズを満たし、あらゆるタイミングファブリック・アーキテクチャ用の優れたソリューションを提供する、という独特の地位にあります。

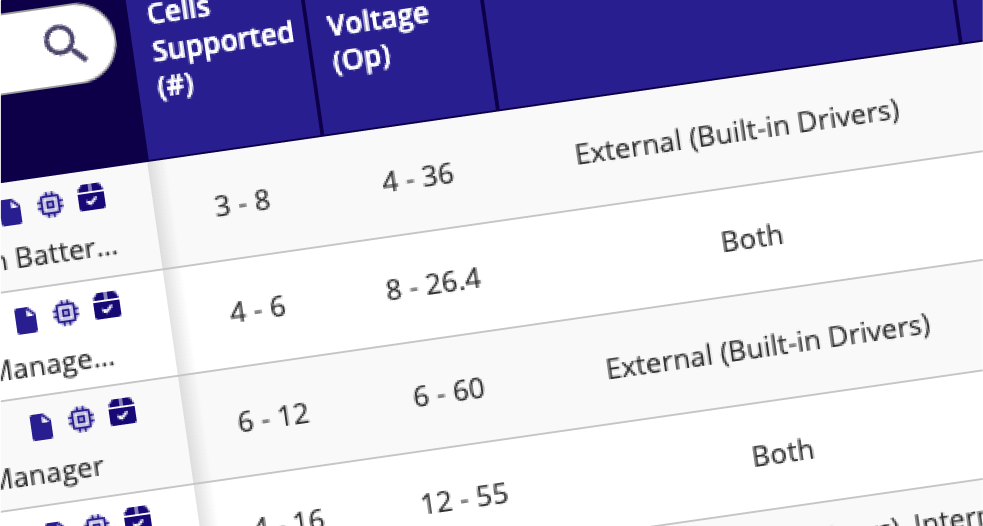

プロダクトセレクタ

プロダクトセレクタ