概要

説明

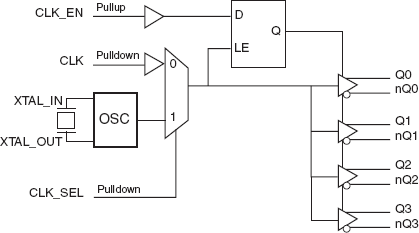

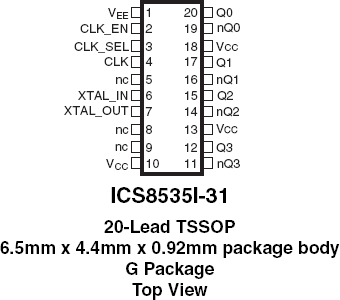

The 8535I-31 is a low skew, high performance 1-to-4 3.3V Crystal Oscillator/LVCMOS-to-3.3V LVPECL fanout buffer. The 8535I-31 has selectable single ended clock or crystal inputs. The single ended clock input accepts LVCMOS or LVTTL input levels and translate them to 3.3V LVPECL levels. The output enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. Guaranteed output and part-to-part skew characteristics make the 8535I-31 ideal for those applications demanding well defined performance and repeatability.

特長

- Four differential 3.3V LVPECL outputs

- Selectable LVCMOS/LVTTL CLK or crystal inputs

- CLK can accept the following input levels: LVCMOS, LVTTL

- Maximum output frequency: 266MHz

- Output skew: 30ps (typical)

- Part-to-part skew: 200ps (maximum)

- Propagation delay: 1.75ns (maximum)

- Additive phase jitter, RMS: 0.057ps (typical)

- Full 3.3V supply mode

- -40°C to 85°C ambient operating temperature

- Replaces the ICS8535I-11

- Available in both standard (RoHS 5) and lead-free (RoHS 6) packages

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

ビデオ&トレーニング

Description

Provides an overview of the features and benefits of IDT's industry-leading fanout buffer and clock distribution portfolio. Fanout buffers are a useful building block of many clock trees, providing signal buffering and multiple low-skew copies of the input signal. The clock fanout from a single input reduces loading on the preceding driver and provides an efficient clock distribution network. Presented by Vik Chaudhry, technical marketing manager at IDT. For more information about Renesas's clock IC timing solutions, visit the Clock Buffers & Drivers page.

Transcript