特長

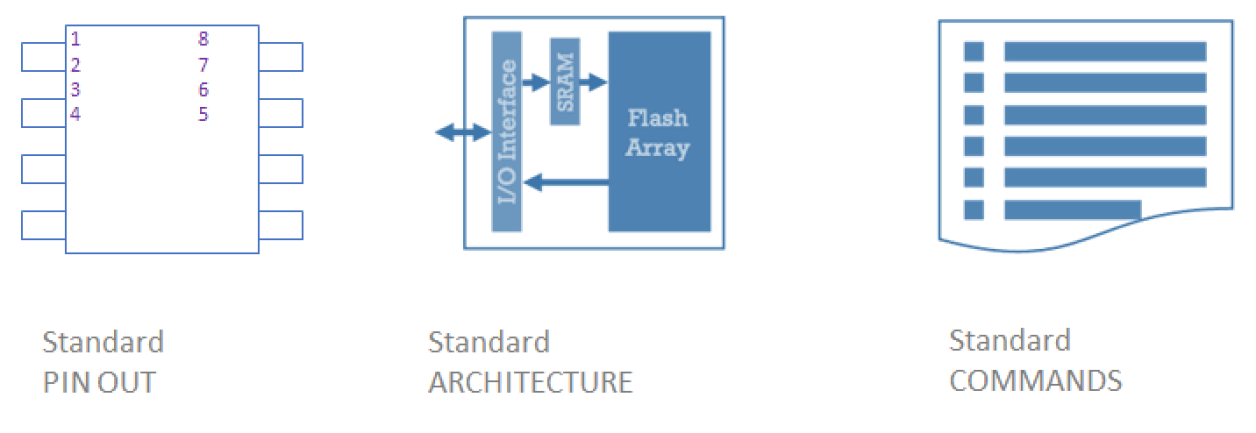

- 汎用互換ピンアウトとコマンド・セット

- 標準ブロックアーキテクチャ

- デュアル I/O、クワッド I/O、XiPの動作に対応

- XiPの連続読み取り、ラップモード及びバーストモード

説明

AT25SF641Bは、当社の標準クラスのコードおよびデータストレージソリューションのひとつで、プログラムコードはフラッシュメモリから内蔵または外部RAMにシャドーイングのうえ、実行される3Vシステム用に設計されています。

このアーキテクチャには、今日のコードおよびデータストレージ・アプリケーションのニーズに合わせて最適化された消去ブロックサイズに加え、ユニークなシリアルデバイス、システムレベルの電子シリアル番号(ESN)ストレージ、ロックされたキーストレージなどのためのセキュリティレジスタの3ページが含まれています。

パラメータ

| 属性 | 値 |

|---|---|

| Memory Class | Standard Flash |

| Memory Density | 64 |

| Operating Voltage Range (V) | 2.7 - 3.6 |

| Speed | 133 MHz |

| Interface | Single, Dual, Quad SPI |

| Temp. Range (°C) | -40 to +85°C |

| Deep Power Down (µA) | 1 |

| Read Current (mA) | 3.3 |

| Key Benefit | Standard features |

アプリケーション・ブロック図

| エッジデバイス用音声ユーザインタフェース (VUI) RA MCUによる音声制御は、スマートデバイスに効率的でネットワークフリーの音声認識を提供します。 |

適用されたフィルター