-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

ClockMatrix™タイミングソリューション

ClockMatrixデバイスファミリは、インタフェース速度が最大800 Gbpsのアプリケーションでクロック設計を簡素化する、高性能かつ高精度のタイミングソリューションです。

ClockMatrixデバイスはシステム内の任意の場所に設置して、クロック発生、周波数変換、ジッタ減衰、位相アライメントなどの重要なタイミング機能を実行できます。デバイスはワイヤレスベースバンド、DU、CU、RU、フロントホールまたはバックホールネットワーク上のIEEE 1588タイムスタンプユニット(TSU)とSyncEポートを正確に同期させるために使用することができます。 このデバイスのファミリは複数の独立したタイミングチャネルをサポートしています。このサポートには、IEEE 1588クロックの合成、SyncEクロックの生成、ジッタの減衰、コンバータのSYSREF生成を含む無線クロックの生成があります。 入力から入力、入力から出力、出力から出力の位相スキューをすべて正確に管理できます。 デバイスは最大112GbpsのSERDES、CPRI/OBSAI、SONET/SDH ADC/DAC、IEEE 1588 TSUなどを直接同期させることができる超低ジッタクロックを出力します。 IEEE 1588システムでの同期を容易に実現するために、ルネサスはPTPクロックマネージャソフトウェアをライセンスに基づき無償で提供しています。

主に次のような特徴があります。

- 柔軟性 – PLLチャネルは個別にシンセサイザ、ジッタ減衰器、またはDCOとして設定可能

- 統合 – 最大8のDPLLと14の出力を単一のパッケージに集約

- 性能 – 88 fs(typ)の低RMSジッタ

- 標準への準拠 – IEEE 1588、OTN、SyncE

- プログラマブル – I2C、SPI、またはOTP

- デバイスの監視 - リファレンス入力、DPLLおよびAPLLロック喪失、ホールドオーバ状態を監視する機能を内蔵

- 用途に適切なサイズ – 144-BGAから48-QFNまでのパッケージを選択可能

主なテクニカルドキュメント: ClockMatrix Family Overview

セレクションテーブル

Function |

Channels (#) |

Inputs (#) |

Diff. Inputs |

Input Freq (MHz) |

Outputs (#) |

Diff. Outputs |

Pkg. Type |

Lead Count (#) |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|

| 型名 | ||||||||||

| IEEE 1588 対応8チャネルシステムシンクロナイザ | System Synchronizer | 8 | 16 | 8 | 0.0000005 - 1000 | 24 | 12 | CABGA | 144 | 54.23 |

| IEEE 1588用4チャネルシステムシンクロナイザ | System Synchronizer | 4 | 14 | 7 | 0.0000005 - 1000 | 16 | 8 | VFQFPN | 72 | 35.53 |

| System Synchronizer for IEEE 1588 - Four Channels | System Synchronizer | 4 | 4 | 2 | 0.0000005 - 1000 | 8 | 4 | VFQFPN | 48 | 41.34 |

| System Synchronizer for IEEE 1588 - Two Channels | System Synchronizer | 2 | 4 | 2 | 0.0000005 - 1000 | 8 | 4 | VFQFPN | 48 | 31.52 |

| System Synchronizer for IEEE 1588 - Four Channels | System Synchronizer | 4 | 4 | 2 | 0.0000005 - 1000 | 24 | 12 | VFQFPN | 72 | |

| Line Card Synchronizer for IEEE 1588 - Eight Channels | Line Card Synchronizer | 8 | 16 | 8 | 0.001 - 1000 | 24 | 12 | CABGA | 144 | 43.8 |

| Line Card Synchronizer for IEEE 1588 - Four Channels | Line Card Synchronizer | 4 | 14 | 7 | 0.001 - 1000 | 16 | 8 | VFQFPN | 72 | 34.81 |

| Line Card Synchronizer for IEEE 1588 - Four Channels | Line Card Synchronizer | 4 | 4 | 2 | 0.001 - 1000 | 8 | 4 | VFQFPN | 48 | |

| Multichannel DPLL / DCO - Eight Channels | Multi-channel DPLL / DCO | 8 | 16 | 8 | 0.001 - 1000 | 24 | 12 | CABGA | 144 | 38.88 |

| Multichannel DPLL / DCO - Four Channels | Multi-channel DPLL / DCO | 4 | 14 | 7 | 0.001 - 1000 | 16 | 8 | VFQFPN | 72 | 28.28 |

| マルチチャネルDPLL/DCO - 4チャネル | Multi-channel DPLL / DCO | 4 | 4 | 2 | 0.001 - 1000 | 8 | 4 | VFQFPN | 48 | 23.93 |

| Multichannel DPLL / DCO - Four / Eight Channels | Multi-channel DPLL / DCO | 8 | 8 | 4 | 0.001 - 1000 | 24 | 12 | VFQFPN | 72 | |

| Multichannel DPLL / DCO - Two / Eight Channels | Multi-channel DPLL / DCO | 8 | 4 | 2 | 0.001 - 1000 | 24 | 12 | VFQFPN | 72 | 25.26 |

| SETS for SyncE and OTN | Multi-channel DPLL / DCO | 4 | 8 | 4 | 0.001 - 1000 | 24 | 12 | VFQFPN | 72 | |

| IEEE 1588対応システムシンクロナイザ - 6チャネル | System Synchronizer | 6 | 8 | 4 | 0.0000005 - 1000 | 24 | 14 | CABGA | 144 | |

| 無線アクセスネットワーク機器用シンクロナイザ - 6チャネル | Multi-channel DPLL / DCO | 6 | 10 | 5 | 0.001 - 1000 | 24 | 12 | VFQFPN | 72 |

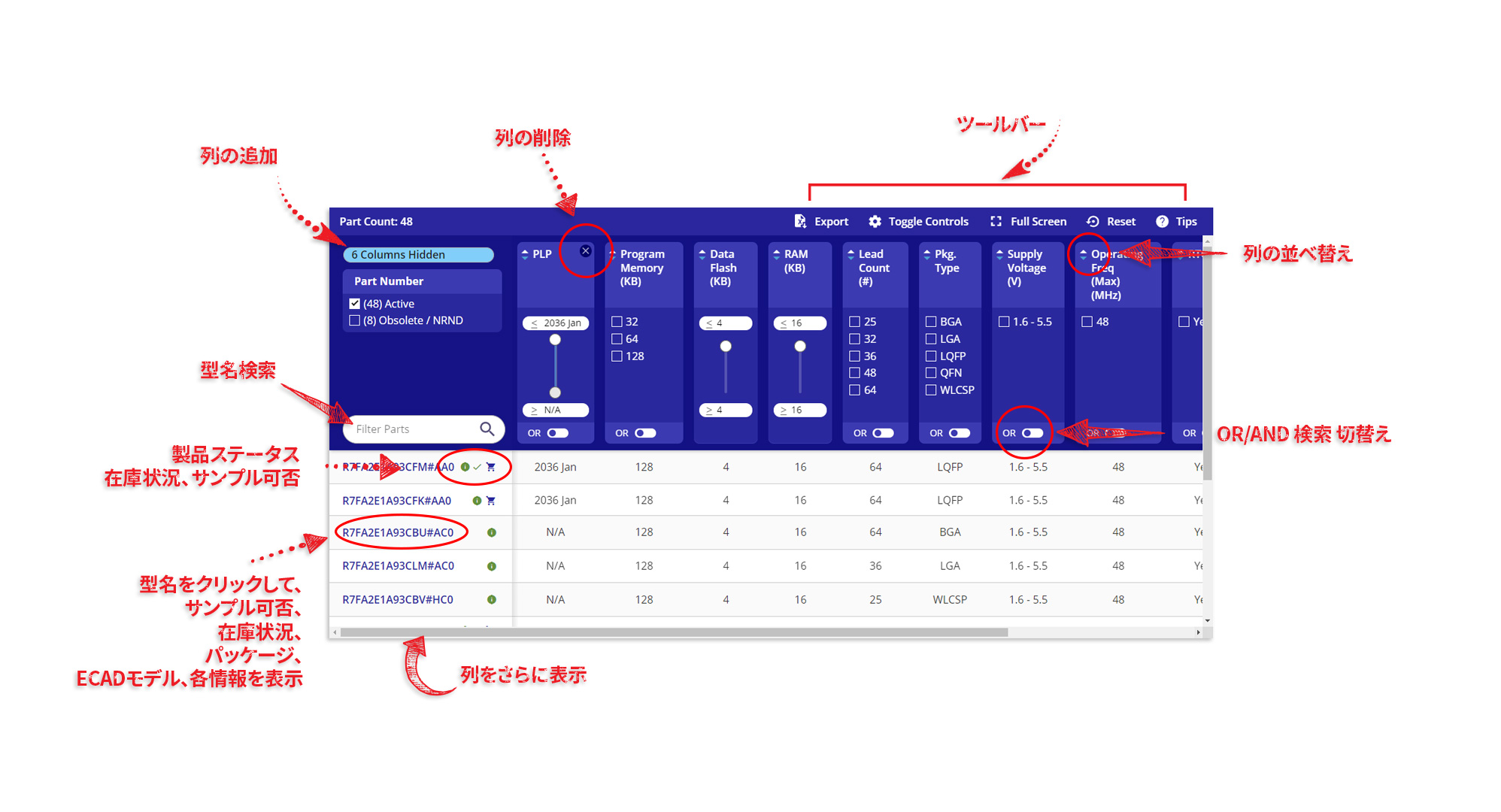

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

ダウンロード

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| ソフトウェア/ツール-その他 | ログインしてダウンロード PDF 488 KB | |

| ソフトウェア/ツール-その他 | ログインしてダウンロード PDF 222 KB | |

2 items

|

||

ビデオ&トレーニング

The ClockMatrix™ 2 family of devices are high-performance, precision timing solutions designed to simplify clock designs for applications with up to 800Gbps interface speeds. This second-generation family delivers improved performance with phase jitter as low as 88fs RMS. The highly integrated devices serve as full-function IEEE 1588 synchronization clocks and ultra-low jitter reference clocks for synchronous Ethernet PHYs with data rates up to 112Gbps PAM-4, reducing design complexity and bill of materials (BOM). Visit renesas.com/clockmatrix to learn more.

ニュース&ブログ

|

タイミングデバイスClockMatrixシンクロナイザが、O-RANの同期プレーン要件であるクラスDに準拠 | ニュース | 2022年9月28日 |

| Selecting the Best Device for Converter Clocking Applications | ブログ | 2022年2月1日 | |

|

通信速度400/800Gbpsの光ネットワークおよび有線ネットワーク向けに、超低ジッタのタイミングデバイスClockMatrix 2ファミリを発売 | ニュース | 2021年12月15日 |

|

Solving Synchronization and Clock Jitter Challenges with ClockMatrix™ 2 for 400Gbps+ Pizza Box Network Switches | ブログ | 2021年11月19日 |

|

Your Guide to Executing pcm4l Software Flawlessly | ブログ | 2021年1月30日 |

|

It’s All About the Bandwidth | ブログ | 2019年3月22日 |