概要

説明

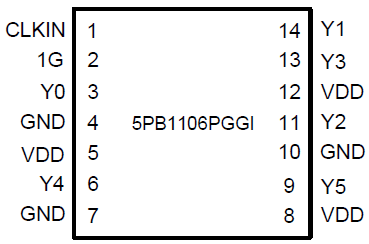

The 5PB1106 is a high-performance 1:6 LVCMOS clock buffer. It has best-in-class Additive Phase Jitter of 50 fsec RMS.

The 5PB1106 also supports an Output Enable function. It is available in 16-pin QFN and 14-pin TSSOP packages and can operate from a 1.8 V to 3.3 V supply.

特長

- High performance 1:6 LVCMOS clock buffer

- Very low pin-to-pin skew <50 ps

- Very low additive jitter <50 fs

- Supply voltage: 1.8 V to 3.3 V

- fmax = 200 MHz

- Integrated serial termination for 50ohm channel

- Packaged in 14-pin TSSOP and small 16-pin QFN packages

- Extended (-40°C to +105°C) temperature range

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

ビデオ&トレーニング

5PB11xx Ultra Low Jitter LVCMOS Buffers

This video provides an overview of the LVCMOS High Performance Clock Buffer Family, highlighting their key features and capabilities.

Video List

ニュース&ブログ

| ブログ | 2018年12月15日 | ||

| IDT社が超低ジッターのLVCMOSクロックバッファ製品ファミリーを開発 | ニュース | 2015年3月30日 |