特長

- 2 - 0.7V current-mode differential CPU pairs

- 1 - 0.7V current-mode differential CPU/PCI-Express selectable pair

- 6 - PCI, 33MHz

- 2 - REF, 14.318MHz

- 3 - 3V66, 66.66MHz

- 1 - 48MHz

- 1 - 24/48MHz

- 5 - PCI-Express 0.7V current mode differential pairs

- CPU outputs cycle-cycle jitter < 85ps

- 3V66 outputs cycle-cycle jitter < 250ps

- PCI outputs cycle-cycle jitter < 500ps

- Programmable output frequency.

- Programmable asynchronous 3V66&PCI frequency.

- Programmable asynchronous PCI-Express frequency.

- Programmable output divider ratios.

- Programmable output skew.

- Programmable spread percentage for EMI control.

- Watchdog timer technology to reset system if system malfunctions.

- Programmable watch dog safe frequency.

- Support I2C Index read/write and block read/write operations.

- Uses external 14.318MHz reference input, external crystal load caps are required for frequency tuning.

説明

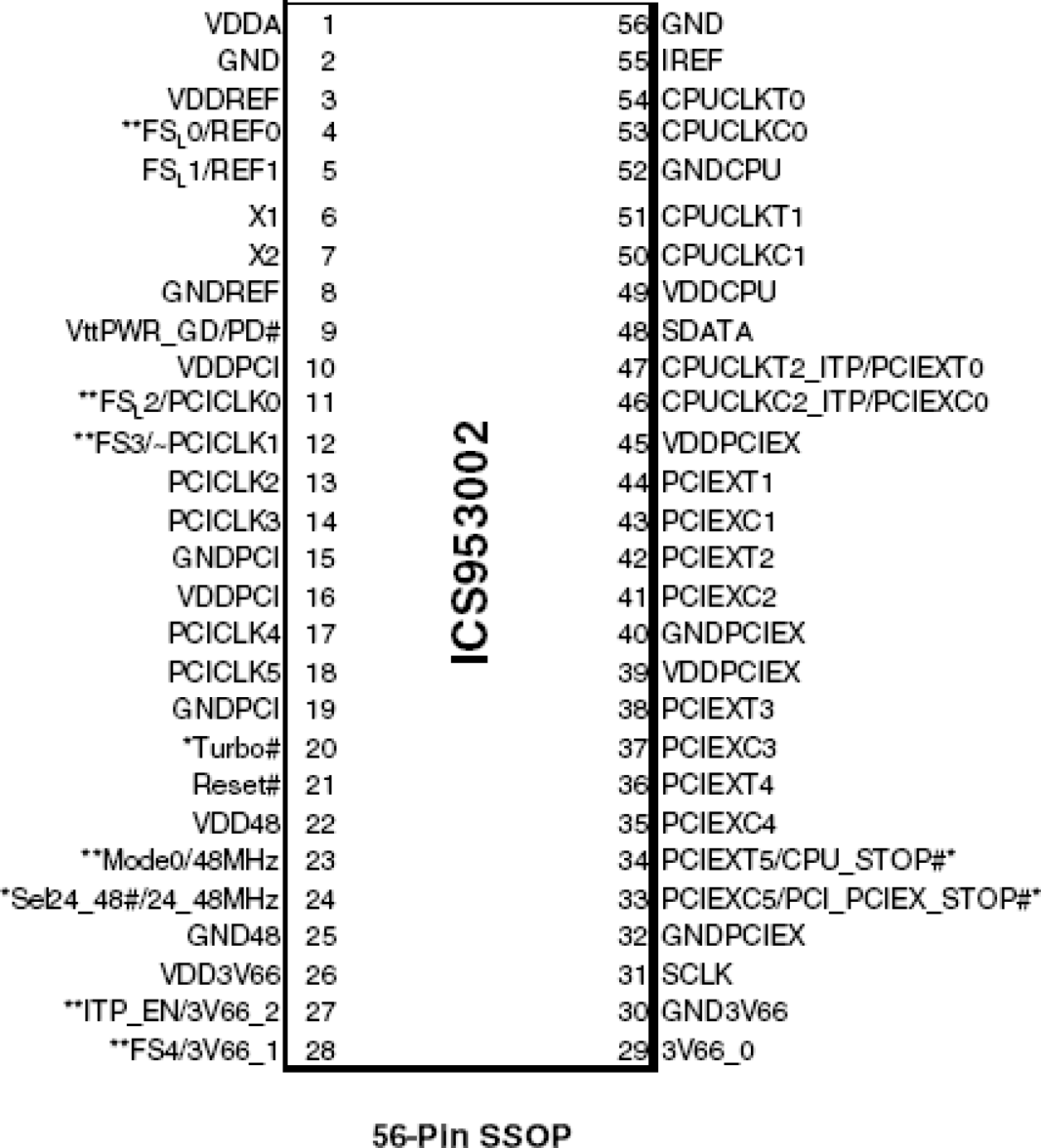

953002 is a 56-pin clock chip for P4 type processors with PCI-Express. The 953002 is part of a whole new line of ICS clock generators and buffers called TCH™ (Timing Control Hub). This part incorporates ICS's newest clock technology which offers more robust features and functionality. Employing the use of a serially programmable I2C interface, this device can adjust the output clocks by configuring the frequency setting, the output divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each individual output clock. M/N control can configure output frequency with resolution up to 0.1MHz increment.

適用されたフィルター