概要

説明

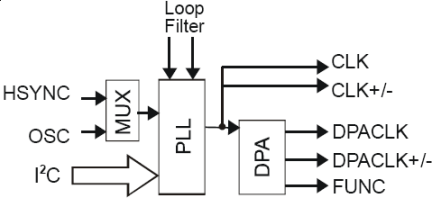

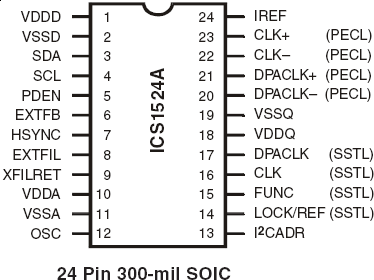

The 1524A is a low-cost, very high-performance frequency generator and phase controlled clock synthesizer. It is perfectly suited to phase controlled clock synthesis and distribution as well as line-locked and genlocked applications. The 1524A offers two channels of clock phase controlled outputs; CLK and DPACLK. These two output channels have both 250 MHz PECL differential and 150 MHz SSTL_3 single-ended output pins. The CLK output channel has a fixed phase relationship to the PLL's input and the DPACLK uses the Dynamic Phase Adjust circuitry to allow control of the clock phase relative to input signal. Optionally, the CLK outputs can operate at half the clock rate and phase aligned with the DPACLK channel, enabling deMUXing of multiplexed analog-to-digital converters. The FUNC pin provides either the regenerated input from the phase-locked loop (PLL) divider chain output or a re-synchronized and sharpened input HSYNC. The advanced PLL uses either its internal programmable feedback divider or an external divider and is programmed by a standard I2C-bus™ serial interface.

特長

- Wide input frequency range

- 8 kHz to 100 MHz

- 250 MHz balanced PECL differential outputs

- 150 MHz single-ended SSTL_3 clock outputs

- Dynamic Phase Adjust (DPA) for DPACLK outputs

- Software controlled phase adjustment

- 360o Adjustment down to 1/64 clock increments

- External or internal loop filter selection

- Uses 3.3 VDC Inputs are 5 volt tolerant.

- I2C-bus serial interface runs at either low speed (100 kHz) or high speed (400 kHz).

- Hardware and Software PLL Lock detection

製品比較

アプリケーション

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 677 KB | |

| EOL通知 | PDF 72 KB | |

| EOL通知 | PDF 72 KB | |

| 製品変更通知 | PDF 361 KB | |

| EOL通知 | PDF 72 KB | |

| EOL通知 | PDF 92 KB | |

| EOL通知 | PDF 388 KB | |

| 製品変更通知 | PDF 223 KB | |

8 items

|

||

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。