H8S/H8SX乗算命令実行サイクル数

| 演算内容 | 実行サイクル数 | |

| H8S | H8SX | |

| 符号なし乗算 16ビット×16ビット→32ビット 8ビット×8ビット→16ビット |

3~4 | 1 |

| 符号付き乗算 16ビット×16ビット→32ビット 8ビット×8ビット→16ビット |

4~5 | 2 |

| 符号なし乗算 RdxRs→Rd(下位32ビット/ 下位16ビット) |

- | 2~5 |

| 符号付き乗算 RdxRs→Rd(下位32ビット/ 下位16ビット) |

- | 2~5 |

| 符号なし乗算 RdxRs→Rd(上位32ビット) |

- | 6 |

| 符号付き乗算 RdxRs→Rd(上位32ビット) |

- | 6 |

H8S/H8SX除算命令実行サイクル数

| 演算内容 | 実行サイクル数 | |

| H8S | H8SX | |

| 符号なし除算 16ビット÷8ビット→商8ビット余り8ビット 32ビット÷16ビット→商16ビット余り16ビット |

12~20 | 10~18 |

| 符号付き除算 16ビット÷8ビット→商8ビット余り8ビット 32ビット÷16ビット→商16ビット余り16ビット |

14~21 | 12~20 |

| 符号なし除算 Rd÷Rs→Rd(商16ビット/ 商32ビット) |

- | 10~18 |

| 符号付き除算 Rd÷Rs→Rd(商16ビット/ 商32ビット) |

- | 11~19 |

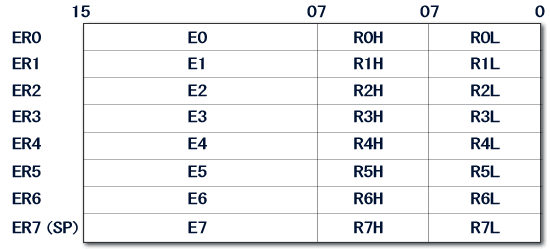

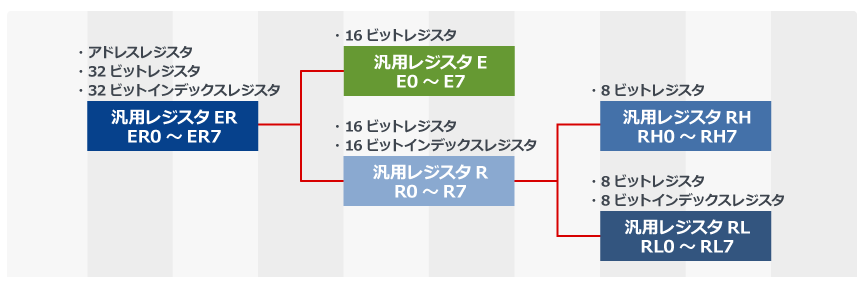

汎用レジスタの構成

汎用レジスタの使用方法

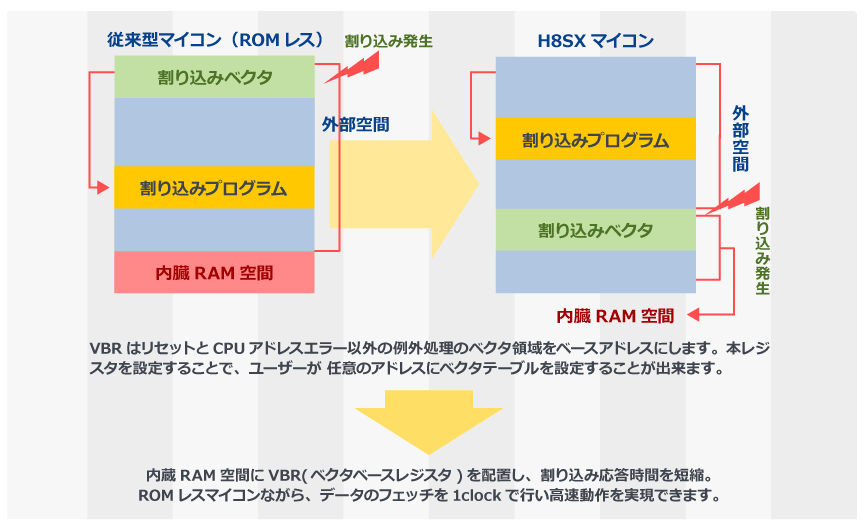

VBR(ベクターレジスタ)使用例

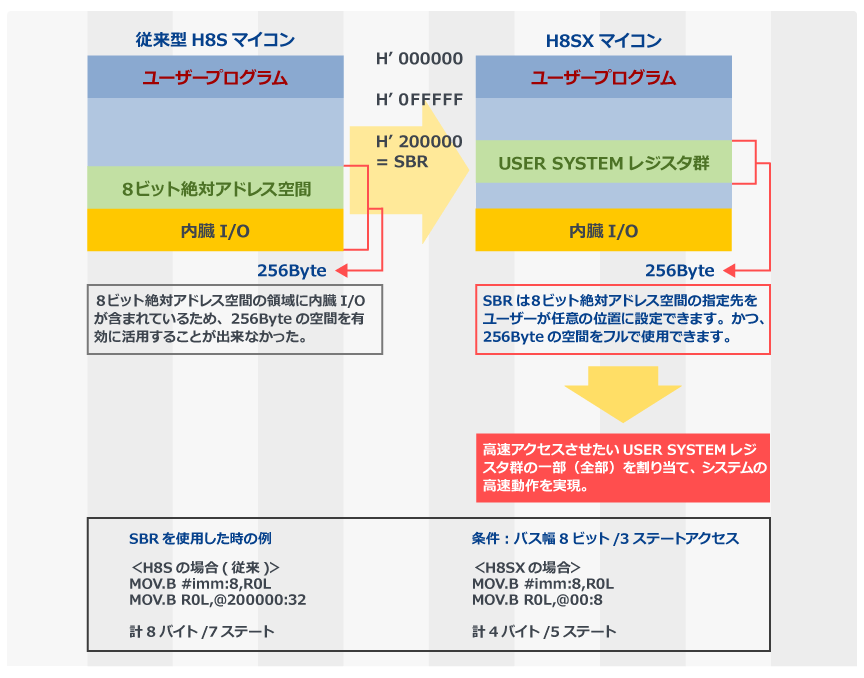

SBR(ショートアドレスレジスタ)

命令

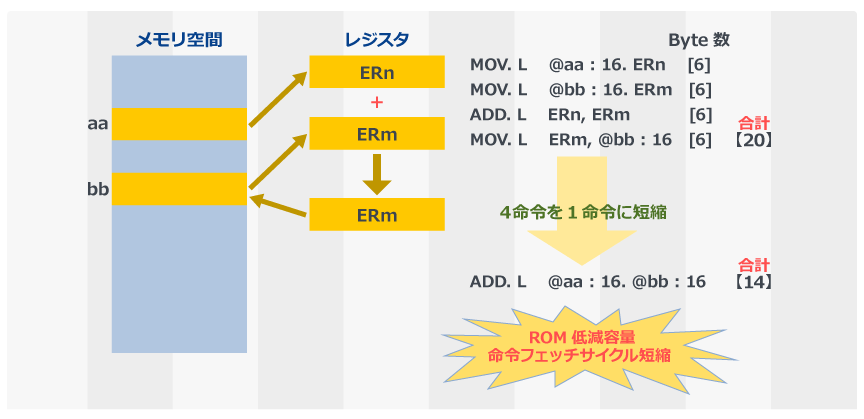

1.メモリに対する演算をサポート

追加命令数 = 基本演算(加減算/ 論理)×基本アドレッシング

例)メモリ上のロングワードサイズデータの加算

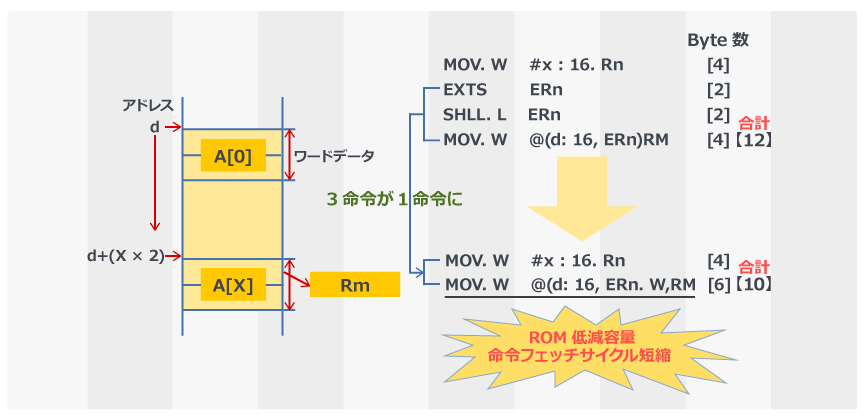

2.アドレッシングモード強化 - 配列用(@(d,Ern,B/W/L))

例)アドレスdからx番目に在るデータをレジスタに書き込む(ワードサイズデータ)

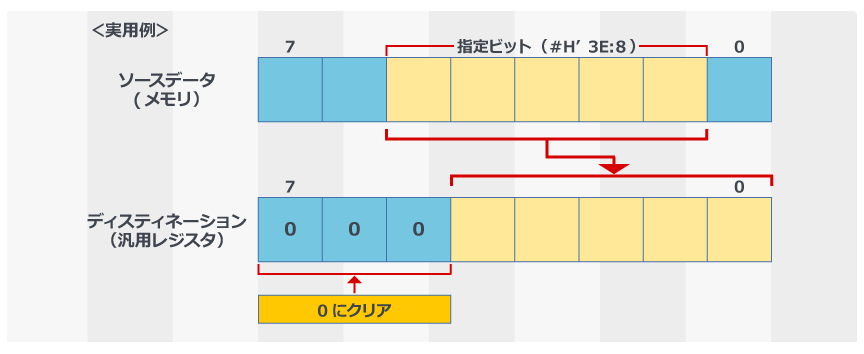

ビットフィールド転送(1)

●BFLD(Bit Field LoaD)

ソースオペランドの指定されたフィールドを下位詰めで、8ビットレジスタRdlに転送します。

ビットフィールドは、8ビットのイミディエートデータの1がセットされているビットで指定されます。