ECU レベルに求められる高速なシミュレータ

近年、自動車では先進運転システムや自動運転などの機能が実現され、ECUに搭載されるソフトウェアの大規模化が進んでいます。このようなECUレベルのソフトウェアのシミュレーションを行う場合、シミュレーション時間が膨大になる傾向にあります。この問題に対してより実行速度の速いシミュレータが求められています。

Renesas QEMU Environment

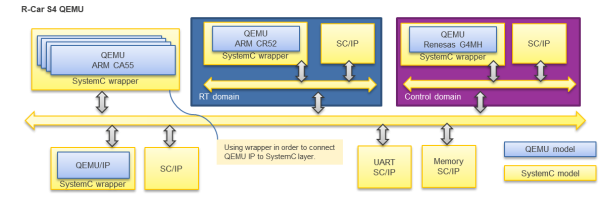

高速なシミュレータを実現するため、ルネサスではQEMUモデルとSystemCモデルを組み合わせたR-Car S4用シミュレータRenesas QEMU Environment(以下、本シミュレータといいます)を開発しています。QEMUのみでシミュレーションする場合は、1種類のCPUアーキテクチャしかシミュレーションできません。しかし、R-Car S4はCA55, CR52, G4MHの3種類の異なるアーキテクチャのCPUを搭載しており、これらCPUを同時にシミュレーションする必要があります。

そこで本シミュレータでは、Fig.1のようにCPUコアのモデルはSystemCモデルのWrapperを使用して実現しています。これはSystemCのWrapperを使うことで、SystemCのインスタンスとして並列処理を実現できるためです。このWrapperでは、QEMUのC言語で準備されたCPUコアモデルからSystemCインターフェイスへの変換やタイミング制御を行います。これにより、本シミュレータでは、3種類のCPUの同時シミュレーションを実現しています。

次に本シミュレータで使用しているQEMUの特徴を以下に示します。

- Dynamic Binary Translation(DBT)による実行速度の高速化

- 抽象度の高いモデルによる実行速度の高速化

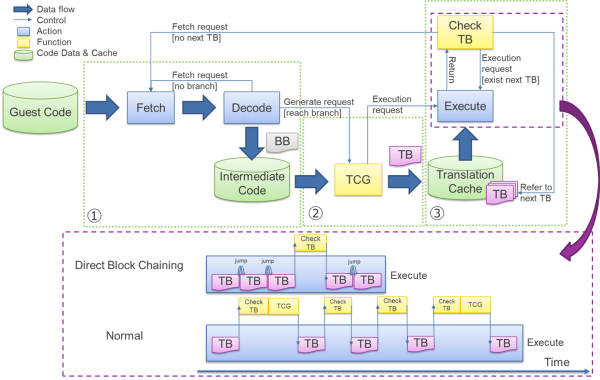

これらの特徴のうちDBTはQEMUのCPUモデルを高速化するための重要な技術です。DBTはQEMU上のCPUで実行するコード(ゲストコード)を短いブロックに分け、シミュレータを実行するPCのCPU(ホストCPU)が実行できるコード(ホストコード)のバイナリに変換しキャッシュします。DBTの実行手順を以下に示します。

- DBTのトランスレーション機能がゲストコードを分岐命令ごとにBasic Block(BB)に分割し、Intermediate Codeにデコードします。Intermediate Codeはゲストコードをホストコードに変換するために利用する中間表現です。

- Tiny Code Generator(TCG)がIntermediate CodeをホストコードのバイナリブロックであるTranslation Block(TB)に変換を行います。変換されたTBはTranslation Cacheに保存されます。

- ホストCPUはTranslation Cacheに保存されたTBを実行します。次に実行するTBがTranslation Cacheにない場合、1.の処理から再度実行します。TBがTranslation Cacheに存在する場合、キャッシュから次のTBを実行します。次の分岐先アドレスが固定の場合、分岐先のTBも決まっているので、Check TBなしで次のTBを実行することができるように、TBの連続性を示すコードを埋め込みます。(Direct Block Chaining)。

ゲストコード実行時は、1.から3.を繰り返し、BBごとにTBに変換された一連の命令を、ホストCPUで実行します。命令ブロックが初めて実行される場合のみ、1.と2.の処理を実行します。既に実行された番地の命令を実行する場合、TBがTranslation Cacheに保存されているため、1.と2.のコード変換処理を省略できます。

また、3.のDirect Block ChainingによってTB同士が接続されることで、ゲストコードのTB変換要求の判定やTranslation Cacheから次のTBを参照する処理を省略します。

このように、本シミュレータはDBTのゲストコードのホストコード変換処理や変換要求を省略し、連続してTBを実行することでCPU実行速度の高速化を実現しています。

Renesas QEMU Environmentの性能

サンプルアプリケーションを用いたR-Car S4の実機とRenesas QEMU EnvironmentのCPUベンチマーク結果をFig.3に示します。Fig.3の結果より、本シミュレータの処理性能(命令実行数)は実機1命令に対して約0.8命令であり、実機に近い処理性能であることが分かります。

R-Car S4 の詳細についてはR-Car S4をご覧ください。

今後の展望

今回はR-Car S4用シミュレータRenesas QEMU Environmentの概要とCPU性能についてご紹介しました。現在のシミュレータはQEMU7.0をベースとしており、QEMU8.0に対応予定です。また、今回はご紹介しませんでしたが、CPU周辺の機能を含めたシミュレーション速度の向上に向け最適化を行っていきます。次世代のプラットフォームにも順次対応し、お客様のソフトウェア開発、システム検討にご利用いただけるよう準備を進めてまいります。