-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

12BIT-2GSPS-REF

circle过时12-Bit, 2GSPS Reference Design using 4 Interleaved 12-Bit, 500MSPS ADCs

概览

简介

NOTICE: The following Reference Design is no longer active

By interleaving Renesas' low power, high sample rate ADCs, it is possible to achieve a combination of ultra-high sample rate and very high dynamic range that is not available in today's stand-alone ADCs.

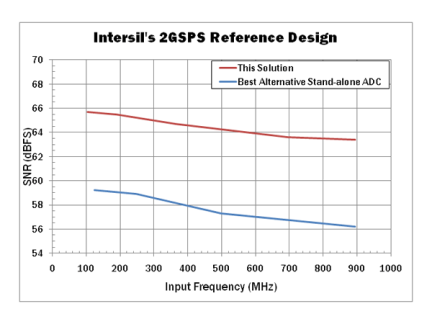

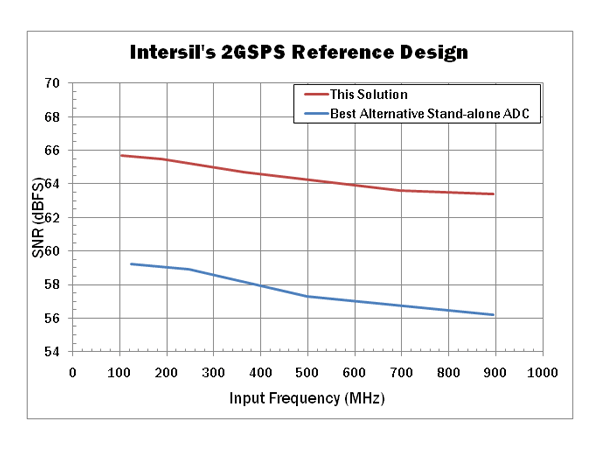

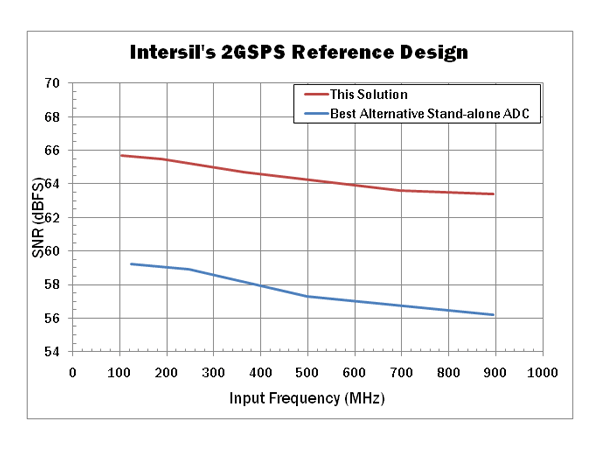

This reference design demonstrates the performance attainable by combining Renesas' ADC technology and SP Devices' interleaving algorithms. In this design, four ISLA112P50 12-bit, 500MSPS analog-to-digital converters are interleaved to sample at a rate of 2.0GSPS. At this sampling rate, the reference design provides over 6dB more SNR and 13dB better SFDR than the best alternative stand-alone ADC.

Disclaimer: THIS MATERIAL IS PROVIDED “AS-IS” FOR EVALUATION PURPOSES ONLY. RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (collectively, “Renesas”) DISCLAIM ALL WARRANTIES, INCLUDING WITHOUT LIMITATION, FITNESS FOR A PARTICULAR PURPOSE AND MERCHANTABILITY. Renesas provides evaluation platforms and design proposals to help our customers to develop products. However, factors beyond Renesas' control, including without limitation, component variations, temperature changes and PCB layout, could significantly affect the product performance. It is the user’s responsibility to verify the actual circuit performance.

特性

- Collaboration of Renesas and SP Devices

- Demonstrates 4-way interleaving of Renesas 500MSPS ISLA112P50S

- Sample rate: 2.0GSPS

- Resolution: 12 bits

- Interleave correction details

- SP Devices' ADX4 provides real-time, digital, FPGA based digital interleave correction of four ISLA112P50s' performance

- Performance

- SNR = 65.5dBfs @ Fin = 190MHz, a 6dB improvement over current best standalone 2GSPS ADCs

- SFDR = 82dBc @ Fin = 190MHz, a 13dB SFDR improvement over current best standalone 2GSPS ADCS

应用

应用

- Radar and electronic/signal intelligence

- Broadband communications

- High-performance data acquisition