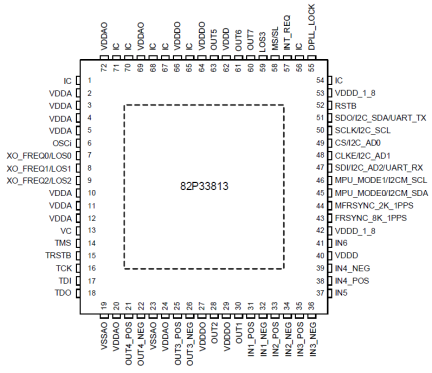

Evaluation Board for 82P33814 Synchronization Management Unit for IEEE 1588 and Synchronous Ethernet

The 82EBP33814 Evaluation board for IEEE 1588 and Synchronous Ethernet allows the user to connect up to four differential ended and up to two single ended reference...