-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

零延迟缓冲器 (ZDB)

零延迟缓冲器 (ZDB) 提供了输出端输入时钟的同步拷贝(无传播延迟),并且一般情况下无需转换频率。 Renesas’ 的 ZDB 均是基于 PLL 的器件,可重新生成带扇出的输入时钟信号,以驱动多个负载提供多种信号级,包括 LVPECL、LVDS、HCSL、CML、HSTL、SSTL 或 LVCMOS。 对于 FPGA、CPU、逻辑和同步存储器等需要同步时钟的应用而言,ZDB 是它们的理想选择。

大多数零延迟缓冲器的延迟可通过外部反馈路径进行调节。 这样可以实现对时钟信号到达负载所需计时的精确控制。 当全部输出(包括反馈输出)均采用简单分频器时,可进行简单的频率转换以保持时钟同步化。

提示: 如果需要不止一个唯一的输出频率(如 100MHz 和 125MHz),可使用“输出库”参数选择器。 每个库与唯一的输出频率对应。

业内领先的零延迟缓冲器解决方案

Renesas' 的零延迟缓冲器 (ZDB) 产品系列拥有广泛的选项和功能。 LVPECL、LVDS、HCSL、CML、HSTL、SSTL 和可选输出等差分输出,都支持高达 3.2GHz 的输出频率和频率高达 350MHz 的单端 LVCMOS 输出。 此外,Renesas' 的 PLL 产品组合中有一些器件支持 1.2V 至 5V 电源电压,可在商业和工业温度范围内使用。

使用 Renesas PLL 产品具有多种好处。 减少电路板上石英晶体的数量,从而提高可靠性,因为晶体很容易受到冲击和振动的影响。 使用时钟信号发生器后,通过使用一个器件取代多个晶体和振荡器,还可降低消费类电子产品'的电路板成本和空间、材料单 (BOM) 和库存水平。 对于包括个人电脑、消费类电子产品或工业系统,以及高性能网络和通信系统在内的各种系统而言,它们都是理想选择。

选择零延迟缓冲器 (ZDB)

选择用于特定应用的 ZDB 时要考虑许多重要因素。 用户可以下列参数作为起始点,来缩小潜在解决方案的范围:

- 输出数量:选择带有足够输出端的 ZDB 来简化您的时钟数。 元件数量减少可简化设计和采购流程,能够更快地投入市场营销,甚至能提高可靠性,从而增加产出。 Renesas 针对高度复杂的系统提供了一些业内’集成度最高的解决方案,同时也针对介于上述两者之间的系统提供了适当的解决方案。

- 输出类型:零延迟缓冲器所需输出的信号类型。 Renesas 提供 LVPECL、LVDS、HCSL、CML、HSTL、SSTL 或 LVCMOS。

- 输入/输出频率范围:输入和输出频率的有效范围。 Renesas 提供的零延迟缓冲器可满足所有主流应用的频率需求。

- 核心电压:向 ZDB 供电的电源电压。 它通常由系统中可用的电源轨决定,并往往会对输出的电压电平产生影响。 Renesas’ 零延迟缓冲器的电压范围为 3.3V 到 1.5V。

产品选型表

Outputs (#) |

Output Type |

Output Freq Range (MHz) |

Input Freq (MHz) |

Inputs (#) |

Input Type |

Output Banks (#) |

Core Voltage (V) |

Output Voltage (V) |

Divider Value |

Output Skew (ps) |

Pkg. Dimensions (mm) |

Pkg. Type |

Lead Count (#) |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 器件号 | |||||||||||||||

| 20-Output DB2000Q PCIe Clock Buffer | 20 | LP-HCSL | 1 - 400 | 1 - 400 | 1 | HCSL | 1 | 3.3 | 0.7 | 50 | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | ||

| 20-Output Enhanced DB2000Q PCIe Clock Buffer | 20 | LP-HCSL | 1 - 400 | 1 - 400 | 1 | HCSL | 1 | 3.3 | 0.7 | 50 | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | ||

| 20-Output DB2000QL PCIe Clock Buffer | 20 | LP-HCSL | 1 - 400 | 1 - 400 | 1 | HCSL | 1 | 3.3 | 0.7 | 50 | 6.0 x 6.0 x 0.85 | VFQFPN | 80 | 3.719 | |

| 20-Output Enhanced DB2000QL PCIe Clock Buffer | 20 | LP-HCSL | 1 - 400 | 1 - 400 | 1 | HCSL | 1 | 3.3 | 0.7 | 50 | 6.0 x 6.0 x 0.85 | VFQFPN | 80 | 3.719 |

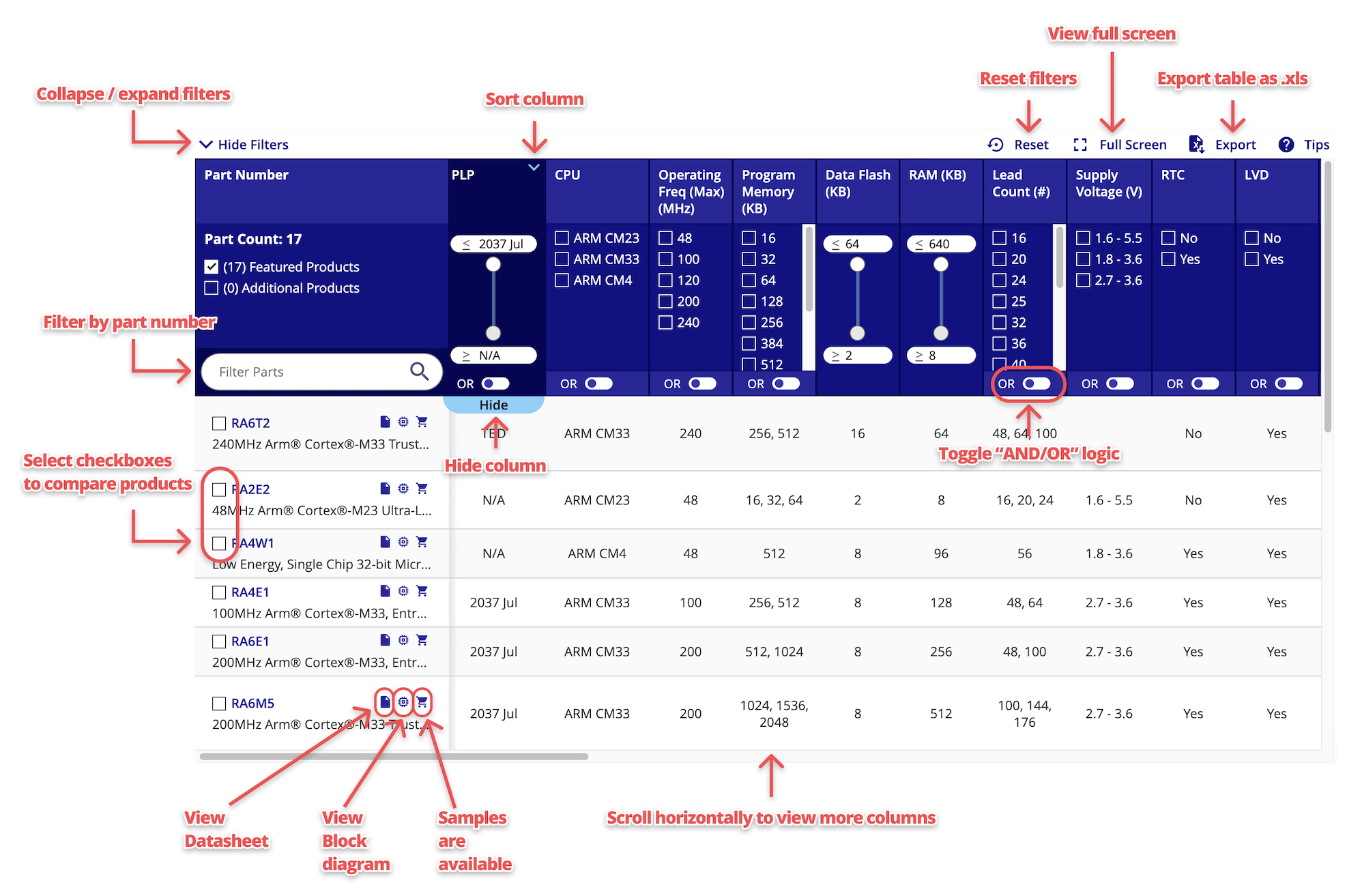

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

视频和培训

Description

Brief overview of IDT's zero-delay buffers. Zero-delay buffers (ZDB) are ideal for applications requiring synchronized clocking for FPGAs, CPUs, logic, and synchronous memory. Zero-delay buffers are PLL-based devices that regenerate the input clock signal with fanout to drive multiple loads. Most devices allow the delay through the device to be adjusted through an external feedback path. This allows precise control of the timing of the clock signals to the loads. Zero-delay buffers provide a synchronous copy of the input clock at the outputs, usually without frequency translation. Simple frequency translation is possible when a single divider is used for all outputs, including feedback output, to maintain clock synchronization. Presented by Vik Chaudhry, technical marketing manager at IDT. For more visit the Zero Delay Buffers page.

Transcript