-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

汽车时钟发生器、缓冲器、振荡器、AEC-Q100、AEC-Q200

瑞萨电子将其在汽车市场的丰富经验与专业时钟知识完美结合,帮助推动汽车电子系统的电子科技进步。 瑞萨电子的VersaClock®汽车时钟发生器是基于锁相环路(PLL)的产品,可为各种应用场景生成一个或多个时钟信号,包括但不限于:信息娱乐、仪表盘、驾驶辅助、平视显示器和ADAS等。

分数输出除法器技术可允许产生任何输出频率组合,即使是没有简单整数关系的组合。 时钟可选单端或差分时钟,并支持最新的PCI-Express和USB接口。 内置一次性可编程(OTP)ROM,确保客户能够定义单个设备,从而根据需要为多个用例供电。

用于信息娱乐或仪表板应用的点钟驱动LCD面板的生成是一个示例用例;其中,VersaClock设备可作为晶体振荡器的一个颇具吸引力的替代品。 得益于VersaClock时钟发生器的高度可配置特性,无论所需的点时钟频率如何,都可以使用单个PCB和BOM,从而减轻频率需求变化时对不同平台的条件限制。

推荐产品

产品选型表

Function |

Outputs (#) |

Output Type |

Output Freq Range (MHz) |

Input Freq (MHz) |

Inputs (#) |

Input Type |

Core Voltage (V) |

Output Voltage (V) |

Output Banks (#) |

Phase Jitter Max RMS (ps) |

C-C Jitter Typ P-P (ps) |

C-C Jitter Max P-P (ps) |

Temp. Range |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 器件号 | |||||||||||||||

| VersaClock® 3S Programmable Clock Generator | Generator | 5 | LP-HCSL, LVCMOS, LVDS, LVPECL | 0.032768 - 500 | 1 - 160 | 1 | Crystal, LP-HCSL, LVCMOS, LVDS, LVPECL | 3.3 | 1.8, 2.5, 3.3 | 3 | 50 | -40 to 85°C, -40 to 105°C | 1.714 | ||

| VersaClock® 3S Programmable Clock Generator | Generator | 7 | LP-HCSL, LVCMOS, LVDS, LVPECL | 0.032768 - 500 | 1 - 160 | 1 | Crystal, LP-HCSL, LVCMOS, LVDS, LVPECL | 3.3 | 1.8, 2.5, 3.3 | 5 | 50 | -40 to 85°C, -40 to 105°C | 1.471 | ||

| VersaClock® 6E Programmable Clock Generator for Automotive | Clock Generator | 5 | HCSL, LVCMOS, LVDS, LVPECL | 1 - 350 | 1 - 350 | 2 | Crystal, HCSL, LVCMOS, LVDS, LVPECL | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 4 | 46 | -40 to 105°C | |||

| 1.8 V to 3.3 V 1:4 LVCMOS High Performance Clock Buffer | Buffer | 4 | LVCMOS | 0 - 200 | 0 - 200 | 1 | LVCMOS | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 1 | -40 to 85°C, -40 to 105°C, -40 to 125°C | 1.259 | |||

| 1.8 V to 3.3 V 1:10 LVCMOS High Performance Clock Buffer | Buffer | 10 | LVCMOS | 0 - 200 | 0 - 200 | 1 | LVCMOS | 1.8, 2.5, 3.3 | 1.8, 2.5, 3.3 | 1 | -40 to 85°C, -40 to 105°C | 2.828 | |||

| AutoClock 车用级可编程时钟发生器 | Generator | 40, 48 | LP-HCSL, LVCMOS, LVDS | 0.001 - 650, 0.001 - 200 | 1 - 650 | 2 | CML, HCSL, LVCMOS, LVDS, LVPECL | 1.8, 3.3 | 1.8, 3.3 | 6, 7 | 34 | 45 | -40 to 105°C | 6.504 | |

| 1000fs Automotive Quartz-based PLL Oscillator | XO | 1 | HCMOS, LVDS, LVPECL | 0.75 - 1350 | 1 | -40 to 85°C, -40 to 105°C, -40° to 105°C | 1.523 |

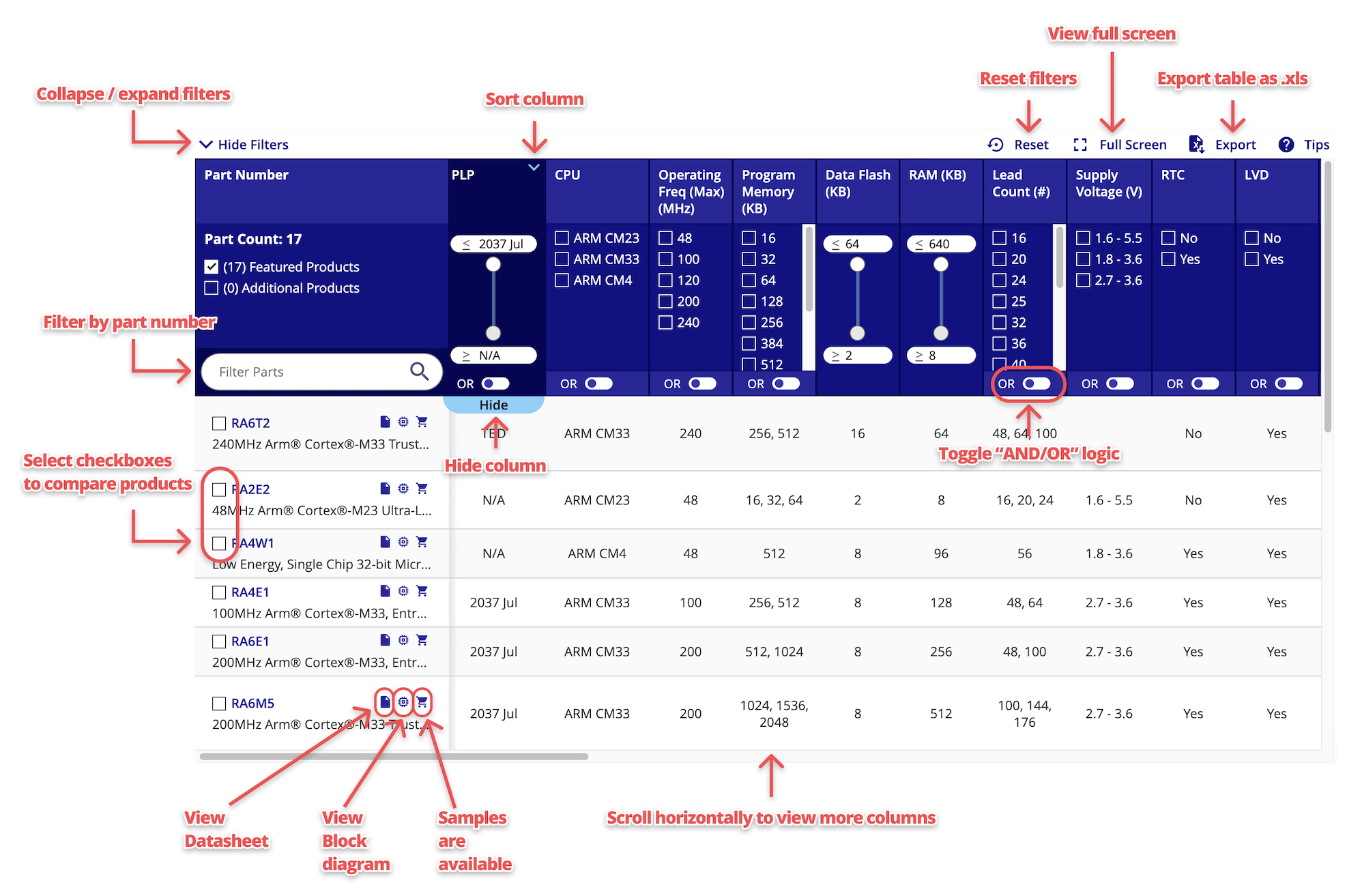

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

视频和培训

了解瑞萨时钟解决方案如何满足系统要求,并提供易于配置的功能。

视频笔录

大家好,我叫 Etienne Winkelmueller,是瑞萨电子负责汽车时钟解决方案的产品线经理。 今天我来和大家聊聊时钟。

就时钟而言,目前的挑战在于随着数据速率的提高和系统复杂性的增加,需要引入一套全新的要求,特别是更高的频率和更低的抖动。

此演示展示了如何使用集成时钟发生器,来创建系统所需的所有时钟。 这个特定只示例展示了瑞萨的 R-Car 系列 SoC,但该示例适用于任何类型的电子系统。

集成时钟发生器具备众多优点。 它们可以生成任何高达 350 兆赫的频率,单端或差分信号以及抖动达到 PCIE Gen 4 水平。 它们还具有展频或频率可重配置等其他功能。

易于配置是该器件最受欢迎的特点。 只需点击网站上的链接,在表格中填写您的技术需求。

用瑞萨集成时钟发生器代替多个晶体振荡器可以获得如下优势:节省占位空间、更丰富的功能、更高的灵活性和更低的成本。