Jitter Attenuator and FemtoClock® Multiplier

概览

简介

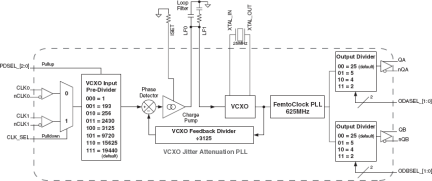

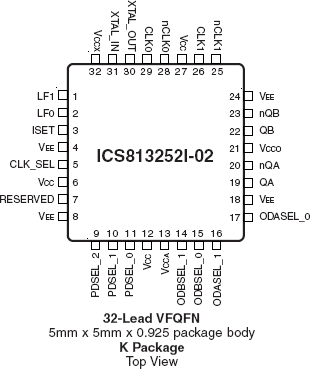

The 813252I-02 is a PLL based synchronous multiplier that is optimized for PDH or SONET to Ethernet clock jitter attenuation and frequency translation. The device contains two internal frequency multiplication stages that are cascaded in series. The first stage is a VCXO PLL that is optimized to provide reference clock jitter attenuation. The second stage is a FemtoClock® frequency multiplier that provides the low jitter, high frequency Ethernet output clock that easily meets Gigabit and 10 Gigabit Ethernet jitter requirements. Pre-divider and output divider multiplication ratios are selected using device selection control pins. The multiplication ratios are optimized to support most common clock rates used in PDH, SONET and Ethernet applications. The VCXO requires the use of an external, inexpensive pullable crystal. The VCXO uses external passive loop filter components which allows configuration of the PLL loop bandwidth and damping characteristics. The device is packaged in a space-saving 32-VFQFN package and supports industrial temperature range.

特性

- Two LVPECL outputs Each output supports independent frequency selection at 25MHz, 125MHz, 156.25MHz and 312.5MHz

- Two differential inputs support the following input types: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Accepts input frequencies from 8kHz to 155.52MHz including 8kHz, 1.544MHz, 2.048MHz, 19.44MHz, 25MHz, 77.76MHz, 125MHz and 155.52MHz

- Attenuates the phase jitter of the input clock by using a low-cost pullable fundamental mode VCXO crystal

- VCXO PLL bandwidth can be optimized for jitter attenuation and reference tracking using external loop filter connection

- FemtoClock frequency multiplier provides low jitter, high frequency output

- Absolute pull range: 50ppm

- FemtoClock VCO frequency: 625MHz

- RMS phase jitter @ 125MHz, using a 25MHz crystal (10kHz '- 20MHz): 1.3ps (maximum)

- 3.3V supply voltage

- -40°C to 85°C ambient operating temperature

- Available inlead-free (RoHS 6) package

产品对比

应用

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.