Package Information

| CAD Model: | View CAD Model |

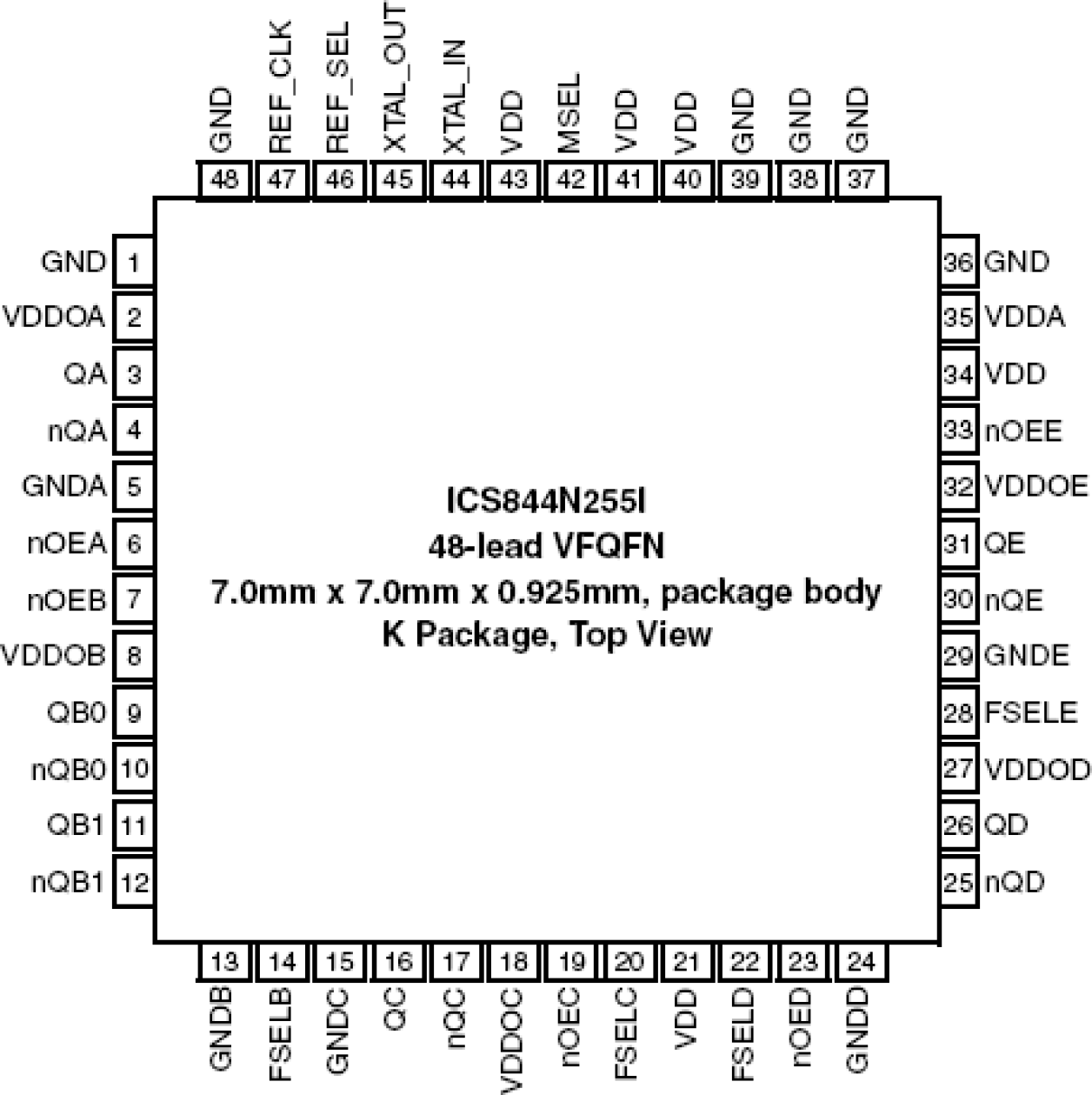

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 0.9 |

| Pitch (mm): | 0.5 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

Product Attributes

| Lead Count (#) | 48 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| C-C Jitter Max P-P (ps) | 6.7 |

| Core Voltage (V) | 2.5 |

| Feedback Input | No |

| Input Freq (MHz) | 25 - 25 |

| Input Type | Crystal, LVCMOS |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 2000 |

| Output Banks (#) | 5 |

| Output Freq Range (MHz) | 25 - 25, 50 - 50, 100 - 100, 125 - 125, 156.25 - 156.25 |

| Output Type | LVDS |

| Output Voltage (V) | 2.5 |

| Outputs (#) | 6 |

| Package Area (mm²) | 49 |

| Phase Jitter Max RMS (ps) | 0.34 |

| Phase Jitter Typ RMS (ps) | 0.25 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Product Category | FemtoClock, Ultra-Low Jitter Clocks (<300 fs RMS) |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | Yes |

| Thickness (mm) | 0.9 |

| Width (mm) | 7 |

Resources for 844N255I

Description

The 844N255I is a 6-output clock synthesizer designed for wireless infrastructure clock applications. The device uses Renesas' fourth generation FemtoClock™ NG technology for an optimum of high clock frequency and low phase noise performance, combined with low power consumption and high power supply noise rejection. The reference frequency is selectable and the following frequency is supported: 25MHz. The synthesizer generates selectable 156.25MHz, 125MHz, 100MHz, 50MHz and 25MHz clock signals. The device is optimized for very low phase noise and cycle-to-cycle jitter. The synthesized clock frequency and the phase-noise performance are optimized for driving SRIO 1.3 and 2.0 SerDes reference, DSP, and host-processor clocks. The device supports a 2.5V voltage supply and is packaged in a small, lead-free (RoHS 6) 48-lead VFQFN package. The extended temperature range supports wireless infrastructure, telecommunication, and networking end equipment requirements.